But the whole direction of scaling is to create more wires, thinner wires and wires which are closer together.

The answer according to Arteris is topology. Arteris’ Kurt Shuler says: “The founders are networking guys and they thought it would be useful to apply networking concepts to chip design.”

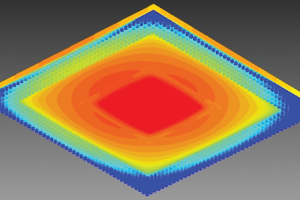

By visualising a bird’s-eye view of the topology the Arteris IP automatically generates a structure which optimises timing and routing.

Arteris claims the benefits of its system are:

- Save one-to-three months of iterations with automatic pipeline insertion

- Save 10%-15% of interconnect area vs. having to overdesign with excessive number of pipelines

- Save two-to-four critical latency cycles by matching timing goals to implementation of each NoC IP version vs. overdesign

- Provide a better starting point for layout process to cut place-and-route cycles and improve layout productivity.

TI, Samsung, Altera and HiSilicon all use the Arteris FlexNOC system.

Electronics Weekly Electronics Design & Components Tech News

Electronics Weekly Electronics Design & Components Tech News