HyperBus Flash Memory Controller

**Highly Configurable**

**Technology Independent**

System Validated

### **Overview**

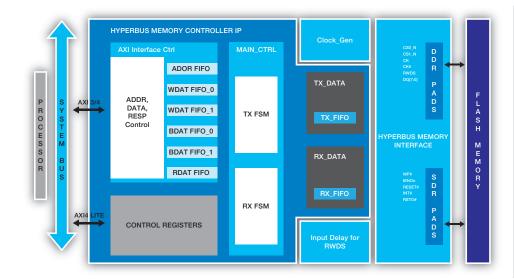

Emerging high-performance applications demand increasingly fast read throughputs from NOR-flash memory devices. At the same time, the pin-count required to implement the memory subsystem should be restricted. Mobiveil's HyperBus flash controller was developed to satisfy the need for higher read/write performance while remaining sensitive to the pin-count constraints of modern microcontrollers. Mobiveil's HyperBus flash controller has the ability to satisfy the memory requirements for both volatile and non-volatile memories in a large swath of high-performance applications.

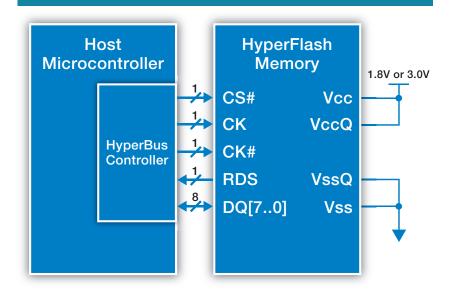

Mobiveil's HyperBus flash Interface is a low pin count interface that achieves significantly higher performance than legacy parallel and SPI interfaces for SPI based NOR flashes. This controller Interface involves a simple read/write protocol that is suitable for both memories and peripheral interfaces. Interestingly, this interface only requires an additional six pins more than the QSPI. The HyperFlash memories coupled with our Hyperbus flash controller provide a new standard for performance by delivering upto 333 MB/s using this 12-pin interface.

# **Features**

- Compatible with spansion hyperbus based memory products

- 0 Wait State Write Burst Operation for HyperBus memory on AXI interface of upto 256 words

- AXI-lite port for control registers accesses

- True Continuous Burst Read operation for HyperFlash on HyperBus memory interface

- Minimum Gap between two Read Operations for highest performance on HyperBus memory interface

- Cache Line accesses for Execution-in-Place (XiP)

- HyperBus memory device clock of upto 166MHz

- Upto 16 outstanding address support in AXI

• Status: Gold

• Availability: Available

• Language : Verilog

• Synthesis : Synopsys DC, Synplicity

• Simulation : Cadence, Synopsys,

Mentor

• Technology: 90nm ASIC or better,

FPGA

# **Specification**

#### **Configurable Options**

- Internal FIFO Depths is configurable

- AXI parameters configurable

#### **Design Attributes**

- Highly modular design

- Clearly demarked clock domains

- Software control for key features

- Loopback for Debugging

#### **Product Package**

- Configurable RTL Code

- HDL based test bench and behavioral models

- Test cases

- Protocol checkers, bus watchers and performance monitors

#### **Documentation**

- Design Guide

- Verification Guide

- Application Note

## **About Mobiveil**

Mobiveil is a fast-growing technology company that specializes in development of Silicon Intellectual Property (SIP), platforms and solutions for AI/ML, Flash Storage, Data Center, 5G Telecom, Automotive and Industrial IOT applications. The Mobiveil team leverages decades of experience to deliver high-quality, production-proven, high-speed serial interconnect SIP cores, and custom and standard form factor embedded platforms to leading companies worldwide. With a highly motivated engineering team, dedicated integration support, a flexible business model, strong industry presence through strategic alliances and key partnerships, Mobiveil solutions add value to users by matching their product goals on time and within budget. Mobiveil is headquartered in Silicon Valley with engineering development centers located in Milpitas, CA, Chennai, Bangalore and Hyderabad, in India, and sales offices and representatives located in the U.S., Europe, Israel, Japan, Taiwan and the People's Republic of China.

# Contact Sales and Support

Mobiveil, Inc 890 Hillview Court, Suite 250 Milpitas, CA - 95035 email: sales@mobiveil.com www.mobiveil.com

Mobiveil, Inc. reserves the right to change this document without prior notice and disclaim all warranties. It is the recipients duty to confirm with Mobiveil, Inc.'s Engineering Department specifications before proceeding with a product design. This document is confidential and should not be reproduced without Mobiveil, Inc.'s approval.

January 2024 | Version 1.2