EFFICIENT EMBEDDED COMPUTING

A DISSERTATION SUBMITTED TO THE DEPARTMENT OF ELECTRICAL ENGINEERING AND THE COMMITTEE ON GRADUATE STUDIES OF STANFORD UNIVERSITY IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

> James David Balfour May 2010

© 2010 by James David Balfour. All Rights Reserved. Re-distributed by Stanford University under license with the author.

This work is licensed under a Creative Commons Attribution-Noncommercial 3.0 United States License. http://creativecommons.org/licenses/by-nc/3.0/us/

This dissertation is online at: http://purl.stanford.edu/nb912df4852

I certify that I have read this dissertation and that, in my opinion, it is fully adequate in scope and quality as a dissertation for the degree of Doctor of Philosophy.

## William Dally, Primary Adviser

I certify that I have read this dissertation and that, in my opinion, it is fully adequate in scope and quality as a dissertation for the degree of Doctor of Philosophy.

## **Mark Horowitz**

I certify that I have read this dissertation and that, in my opinion, it is fully adequate in scope and quality as a dissertation for the degree of Doctor of Philosophy.

## **Christoforos Kozyrakis**

Approved for the Stanford University Committee on Graduate Studies.

## Patricia J. Gumport, Vice Provost Graduate Education

This signature page was generated electronically upon submission of this dissertation in electronic format. An original signed hard copy of the signature page is on file in University Archives.

## Abstract

Embedded computer systems are ubiquitous, and contemporary embedded applications exhibit demanding computation and efficiency requirements. Meeting these demands presently requires the use of application-specific integrated circuits and collections of complex system-on-chip components. The design and implementation of application-specific integrated circuits is both expensive and time consuming. Most of the effort and expense arises from the non-recurring engineering activities required to manually lower high-level descriptions of systems to equivalent low-level descriptions that are better suited to hardware realization. Programmable systems, particularly those that can be targeted effectively using high-level programming languages, offer reduced development costs and faster design times. They also offer the flexibility required to upgrade previously deployed systems as new standards and applications are developed. However, programmable systems are less efficient than fixed-function hardware. This significantly limits the class of applications for which programamble processors are an acceptable alternatives to application-specific fixed-function hardware, as efficiency demands often preclude the use of programmable hardware. With most contemporary computer systems limited by efficiency, improving the efficiency of programmable systems is a critical challenge and an active area of computer systems research.

This dissertation describes Elm, an efficient programmable system for high-performance embedded applications. Elm is significantly more efficient than conventional embedded processors on compute-intensive kernels. Elm allows software to exploit parallelism to achieve performance while managing locality to achieve efficiency. Elm implements a novel distributed and hierarchical system organization that allows software to exploit the abundant parallelism, reuse, and locality that are present in embedded applications. Elm provides a variety of mechanisms to assist software in mapping applications efficiently to massively parallel systems. To improve efficiency, Elm allows software to explicitly schedule and orchestrate the movement and placement of instructions and data.

This dissertation proposes and critically analyzes concepts that encompass the interaction of computer architecture, compiler technology, and VLSI circuits to increase performance and efficiency in modern embedded computer systems. A central theme of this dissertation is that the efficiency of programmable embedded systems can be improved significantly by exposing deep and distributed storage hierarchies to software. This allows software to exploit temporal and spatial reuse and locality at multiple levels in applications in order to reduce instruction and data movement.

## Acknowledgments

First, I would like to thank my dissertation advisor, Professor William J. Dally, who has been great mentor and teacher. I benefited immensely from Bill's technical insight, vast experience, boundless enthusiasm, and steadfast support.

I would like to thank the other members of my dissertation committee, Professors Mark Horowitz, Christos Kozyrakis, and Boris Murmann. I had the distinct pleasure of having all three as lecturers at various times while a graduate student, and benefited greatly from their insights and experience. I imagine all will recognize some aspects of their teaching and influence within this dissertation.

I was fortunate to befriend some fantastic folks while at Stanford. In particular, I would like to thank Michael Linderman for years of engaging early morning discussions, and Catie Chang for years of engaging late night discussions and encouragement; my first few years at Stanford would not have been nearly as tolerable without their friendship. I would like the thank James Kierstead for several years of Sunday mornings spent discussing the plight of graduate students over waffles and coffee.

I particularly want to thank Tanya for her friendship, patience, support, assistance, and understanding. The last year would have been difficult without her.

I should like to acknowledge the other members of the concurrent VLSI architecture group at Stanford that I had the benefit of interacting with. In particular, I would like to acknowledge the efforts of the other members of the efficient embedded computing group. In approximate chronological order: David Black-Schaffer, Jongsoo Park, Vishal Parikh, R. Curtis Harting, and David Sheffield. I also had the pleasure of sharing an office with Ted Jiang, which I appreciated. Ted was always around and cheery on weekends, which made Sundays in the office more enjoyable, and kept the bookshelves well stocked.

While a student at Stanford, I was funded in part by a Stanford Graduate Fellowship that was endowed by Cadence Design Systems. I remain grateful for the support.

Finally, I would like to thank my family for all the love and support they have provided through the years.

# Contents

| A | ostrac | t                                                  | iv |

|---|--------|----------------------------------------------------|----|

| A | know   | ledgments                                          | v  |

| 1 | Intr   | oduction                                           | 1  |

|   | 1.1    | Embedded Computing                                 | 2  |

|   | 1.2    | Technology and System Trends                       | 4  |

|   | 1.3    | A Simple Problem of Productivity and Efficiency    | 5  |

|   | 1.4    | Collaboration and Previous Publications            | 6  |

|   | 1.5    | Dissertation Contributions                         | 6  |

|   | 1.6    | Dissertation Organization                          | 8  |

| 2 | Con    | temporary Embedded Architectures                   | 10 |

|   | 2.1    | The Efficiency Impediments of Programmable Systems | 10 |

|   | 2.2    | Common Strategies for Improving Efficiency         | 16 |

|   | 2.3    | A Survey of Related Contemporary Architectures     | 20 |

|   | 2.4    | Chapter Summary                                    | 23 |

| 3 | The    | Elm Architecture                                   | 24 |

|   | 3.1    | Concepts                                           | 24 |

|   | 3.2    | System Architecture                                | 25 |

|   | 3.3    | Programming and Compilation                        | 32 |

|   | 3.4    | Chapter Summary                                    | 36 |

| 4 | Inst   | ruction Registers                                  | 37 |

|   | 4.1    | Concepts                                           | 37 |

|   | 4.2    | Microarchitecture                                  | 44 |

|   | 4.3    | Examples                                           | 47 |

|   | 4.4    | Allocation and Scheduling                          | 59 |

|   | 4.5    | Evaluation and Analysis                            | 67 |

|   | 4.6    | Related Work                                       | 78 |

|   | 4.7  | Chapter Summary                                | 80  |

|---|------|------------------------------------------------|-----|

| 5 | Ope  | rand Registers and Explicit Operand Forwarding | 81  |

|   | 5.1  | Concepts                                       | 81  |

|   | 5.2  | Microarchitecture                              | 85  |

|   | 5.3  | Example                                        | 87  |

|   | 5.4  | Allocation and Scheduling                      | 89  |

|   | 5.5  | Evaluation                                     | 94  |

|   | 5.6  | Related Work                                   | 102 |

|   | 5.7  | Chapter Summary                                | 102 |

| 6 | Inde | exed and Address-Stream Registers              | 104 |

|   | 6.1  | Concepts                                       | 104 |

|   | 6.2  | Microarchitecture                              | 106 |

|   | 6.3  | Examples                                       | 113 |

|   | 6.4  | Evaluation and Analysis                        | 122 |

|   | 6.5  | Related Work                                   | 128 |

|   | 6.6  | Chapter Summary                                | 131 |

| 7 | Ense | embles of Processors                           | 132 |

|   | 7.1  | Concept                                        | 132 |

|   | 7.2  | Microarchitecture                              | 137 |

|   | 7.3  | Examples                                       | 139 |

|   | 7.4  | Allocation and Scheduling                      | 143 |

|   | 7.5  | Evaluation and Analysis                        | 146 |

|   | 7.6  | Related Work                                   | 149 |

|   | 7.7  | Chapter Summary                                | 152 |

| 8 | The  | Elm Memory System                              | 153 |

|   | 8.1  | Concepts                                       | 153 |

|   | 8.2  | Microarchitecture                              | 165 |

|   | 8.3  | Example                                        | 177 |

|   | 8.4  | Evaluation and Analysis                        | 179 |

|   | 8.5  | Related Work                                   | 189 |

|   | 8.6  | Chapter Summary                                | 191 |

| 9 | Con  | clusion                                        | 192 |

|   | 9.1  | Summary of Thesis and Contributions            | 192 |

|   | 9.2  | Future Work                                    | 193 |

| A | Exp         | erimental Methodology                             | 196 |

|---|-------------|---------------------------------------------------|-----|

|   | A.1         | Performance Modeling and Estimation               | 196 |

|   | A.2         | Power and Energy Modeling                         | 197 |

| B | Desc        | criptions of Kernels and Benchmarks               | 200 |

|   | <b>B</b> .1 | Description of Kernels                            | 200 |

|   | B.2         | Benchmarks                                        | 204 |

| С | Elm         | Instruction Set Architecture Reference            | 206 |

|   | C.1         | Control Flow and Instruction Registers            | 206 |

|   | C.2         | Operand Registers and Explicit Operand Forwarding | 210 |

|   | C.3         | Indexed Registers and Address-Stream Registers    | 213 |

|   | C.4         | Ensembles and Processor Corps                     | 217 |

|   |             | Memory System                                     |     |

|   |             |                                                   |     |

## Bibliography

# **List of Tables**

| 1.1        | Estimates of Energy Expended Performing Common Operations | 7   |

|------------|-----------------------------------------------------------|-----|

| 2.1<br>2.2 | Embedded RISC Processor Information                       |     |

| 4.1        | Elm Instruction Fetch Energy                              | 76  |

| 5.1        | Energy Consumed by Common Operations                      | 87  |

| 8.1<br>8.2 | Execution Times and Data Transferred                      |     |

| C.1        | Mapping of Message Registers to Communication Links       | 218 |

# **List of Figures**

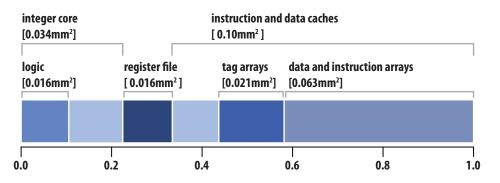

| 2.1  | Embedded RISC Processor Area                                                      | 12 |

|------|-----------------------------------------------------------------------------------|----|

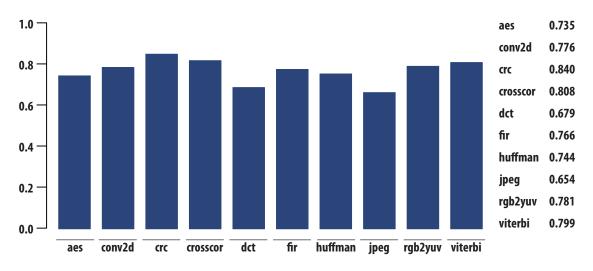

| 2.2  | Average Instructions Per Cycle for an Embedded RISC Processor                     | 12 |

| 2.3  | Energy Consumption by Module for an Embedded RISC Processor                       | 13 |

| 2.4  | Distribution of Instructions by Operation Type in Embedded Kernels                | 14 |

| 2.5  | Distribution of Instructions within Embedded Kernels                              | 15 |

| 2.6  | Distribution of Energy Consumption within Embedded Kernels                        | 16 |

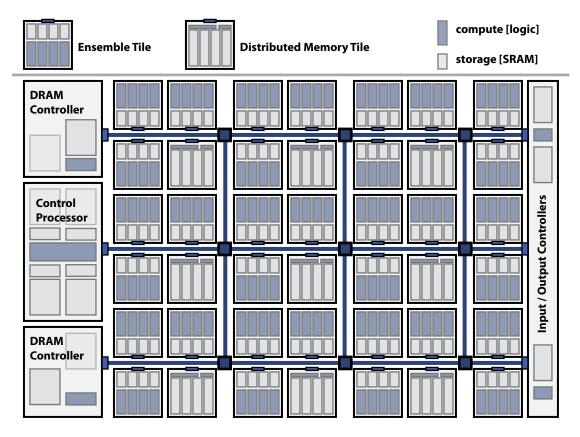

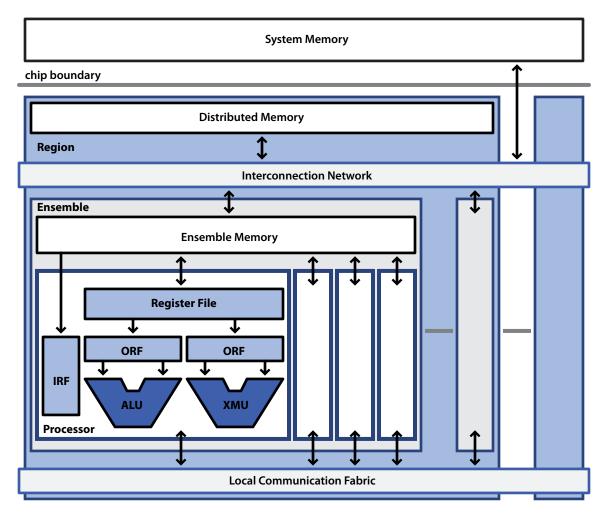

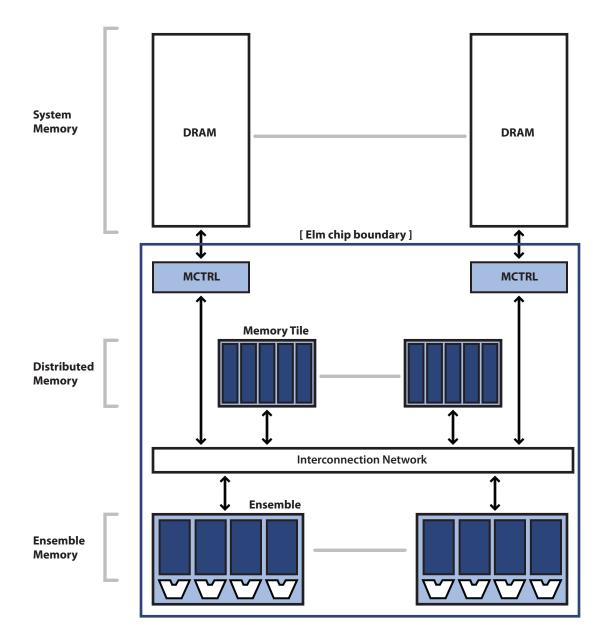

| 3.1  | Elm System Architecture                                                           | 25 |

| 3.2  | Elm Communication and Storage Hierarchy                                           | 26 |

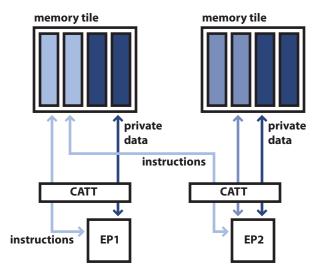

| 3.3  | Elk Actor Concept                                                                 | 33 |

| 3.4  | Elk Bundle Concept                                                                | 34 |

| 3.5  | Elk Stream Concept                                                                | 34 |

| 3.6  | Elk Implementation of FFT                                                         | 35 |

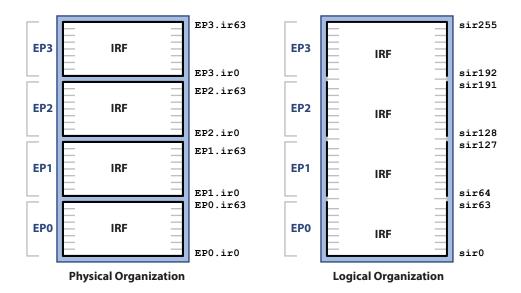

| 4.1  | Instruction Register Organization                                                 | 38 |

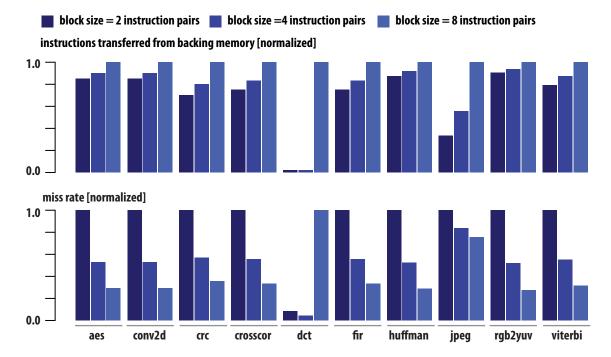

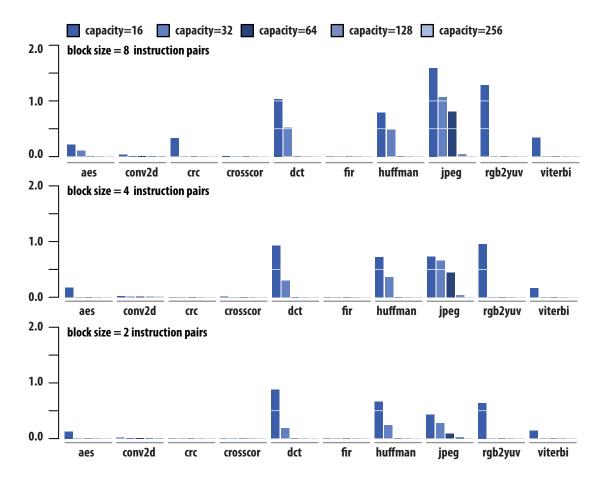

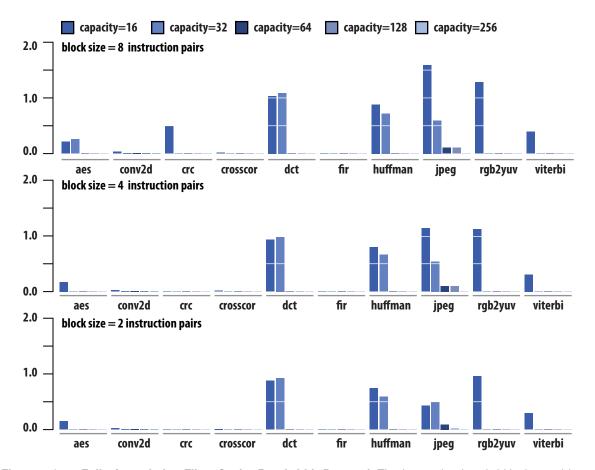

| 4.2  | Impact of Cache Block Size on Miss Rate and Instructions Transferred              | 43 |

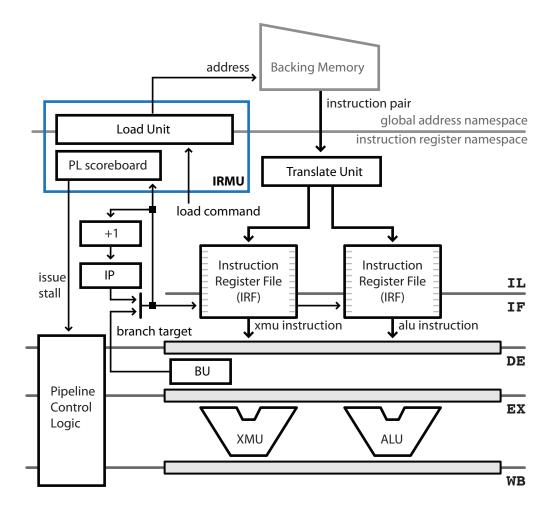

| 4.3  | Instruction Register Microarchitecture                                            | 45 |

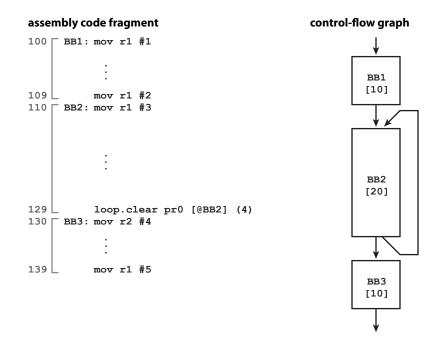

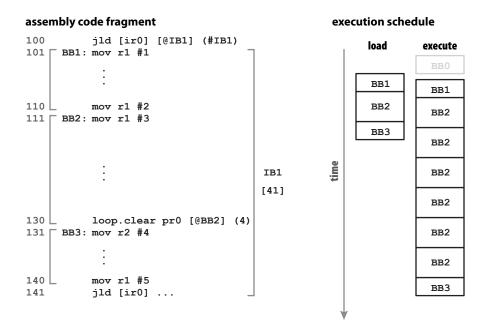

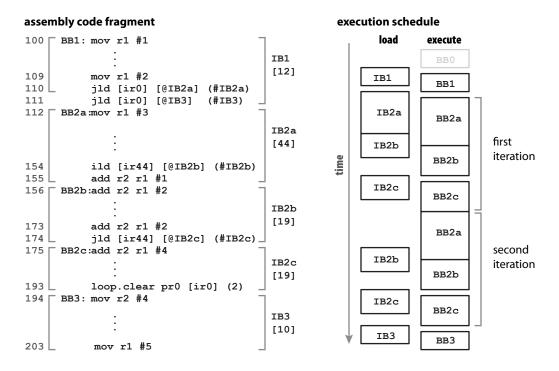

| 4.4  | Assembly Code Fragment of a Loop that can be Captured in Instruction Registers    | 48 |

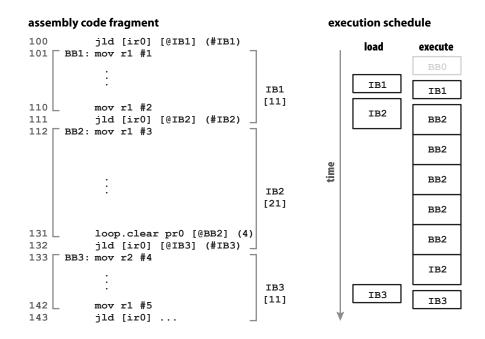

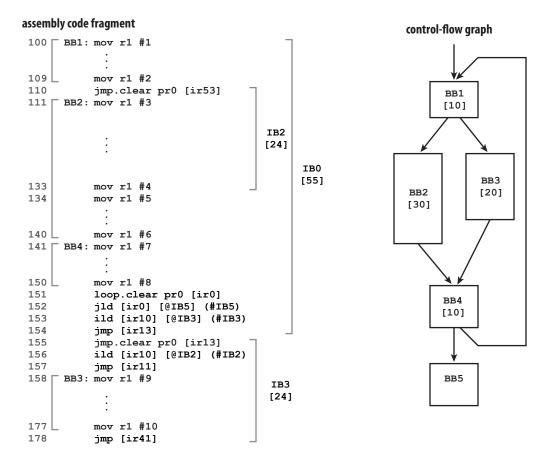

| 4.5  | Assembly Code Produced with a Simple Allocation and Scheduling Strategy           | 49 |

| 4.6  | Assembly Code Fragment Produced when Instruction Load is Advanced                 | 50 |

| 4.7  | Assembly Code Fragment with a Loop that Exceeds the Instruction Register Capacity | 51 |

| 4.8  | Loop after Basic Instruction Load Scheduling                                      | 52 |

| 4.9  | Assembly Code After Partitioning Loop Body Into 3 Basic Blocks                    | 53 |

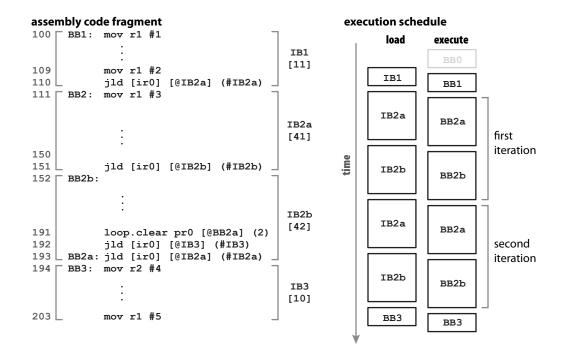

| 4.10 | Assembly Code After Load Scheduling                                               | 54 |

| 4.11 | Assembly Code Fragment Illustrating a Procedure Call                              | 55 |

| 4.12 | Assembly Code Fragment Illustrating Function Call Using Function Pointer          | 56 |

| 4.13 | Assembly Code Illustrating Indirect Jump                                          | 57 |

| 4.14 | Assembly Fragment Containing a Loop with a Control-Flow Statement                 | 58 |

| 4.15 | Contents of Instruction Registers During Loop Execution                           | 59 |

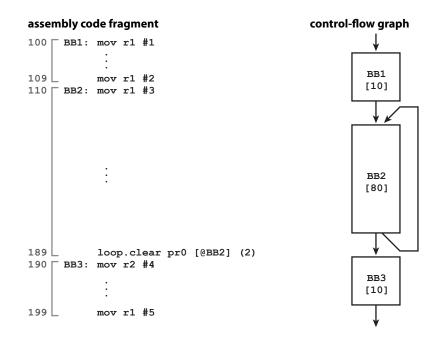

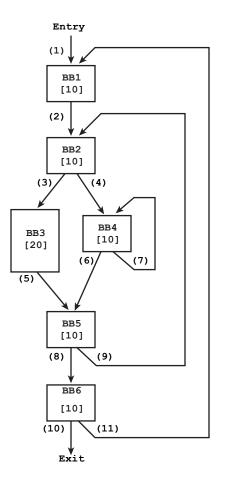

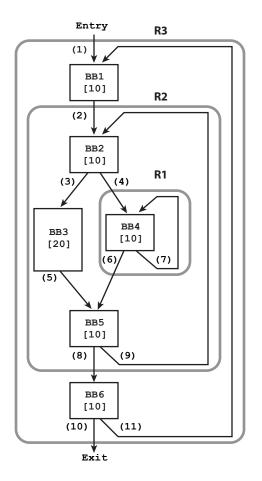

| 4.16 | Control-Flow Graph                                                                | 60 |

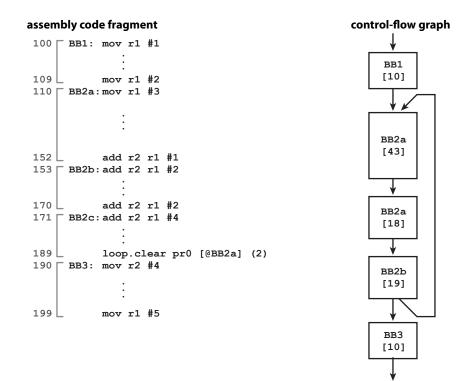

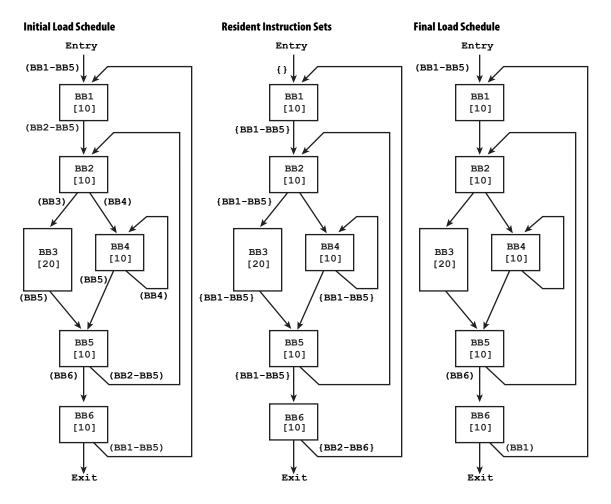

| 4.17 | Illustration of Regions in the Control-Flow Graph                                     | 62  |

|------|---------------------------------------------------------------------------------------|-----|

| 4.18 | Resident Instruction Sets                                                             | 64  |

| 4.19 | Kernel Code Size After Instruction Register Allocation and Scheduling                 | 67  |

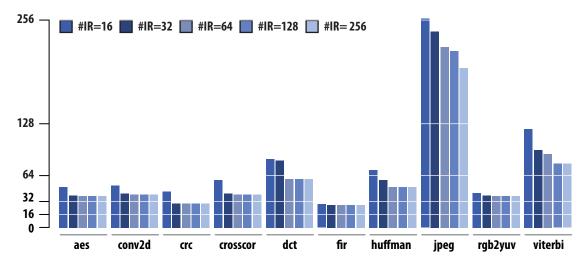

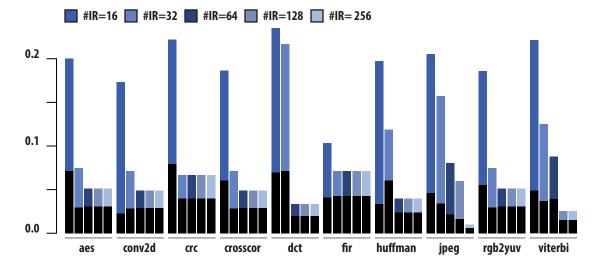

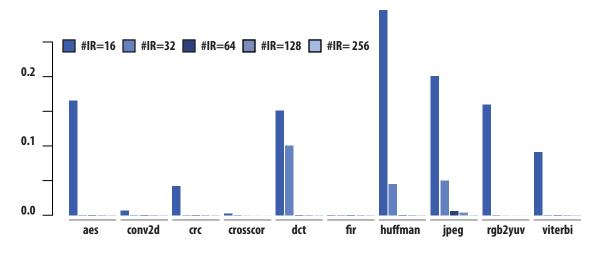

| 4.20 | Static Fraction of Instruction Pairs that Load Instructions                           | 68  |

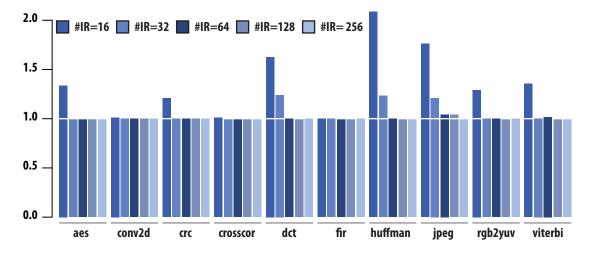

| 4.21 | Normalized Kernel Execution Time                                                      | 69  |

| 4.22 | Fraction of Issued Instruction Pairs that Contain Instruction Loads                   | 70  |

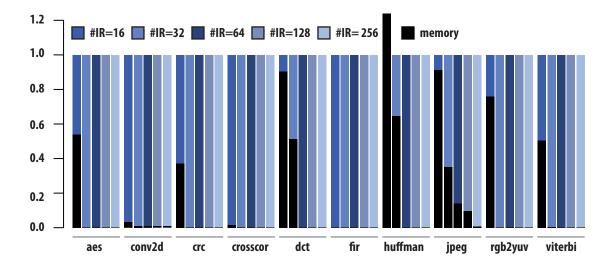

| 4.23 | Normalized Instruction Bandwidth Demand                                               | 71  |

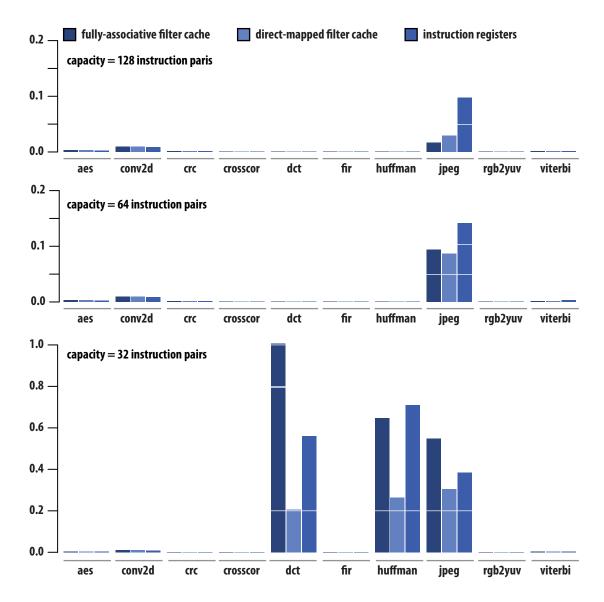

| 4.24 | Direct-Mapped Filter Cache Bandwidth Demand                                           | 73  |

| 4.25 | Fully-Associative Filter Cache Bandwidth Demand                                       | 74  |

| 4.26 | Comparison of Instructions Loaded Using Filter Caches and Instruction Registers       | 75  |

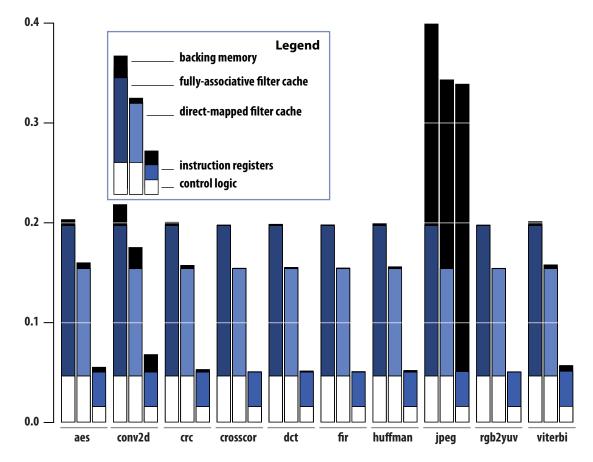

| 4.27 | Instruction Delivery Energy                                                           | 77  |

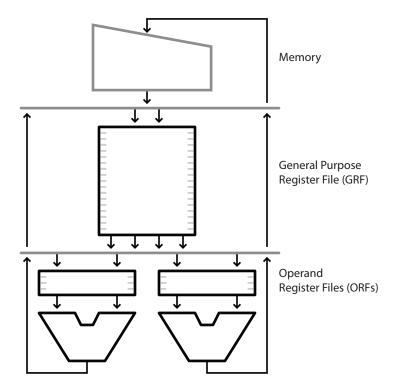

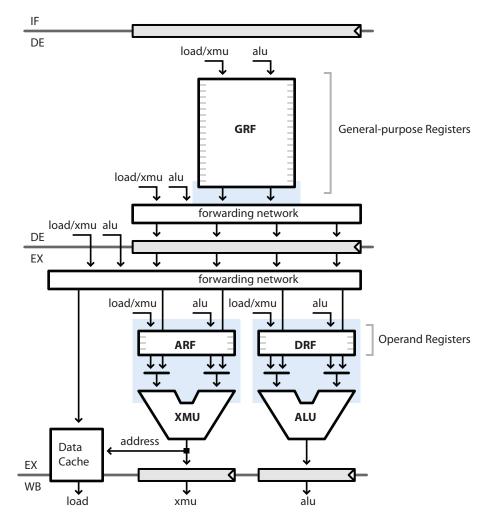

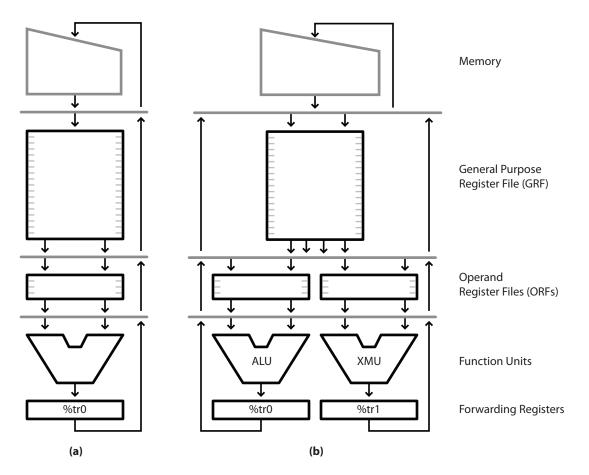

| 5.1  | Operand Register Organization                                                         | 84  |

| 5.2  | Operand Register Microarchitecture                                                    | 86  |

| 5.3  | Intermediate Representation                                                           | 88  |

| 5.4  | Assembly for Conventional Register Organization                                       | 88  |

| 5.5  | Assembly Using Explicit Forwarding and Operand Registers                              | 89  |

| 5.6  | Calculation of Operand Appearances                                                    | 92  |

| 5.7  | Calculation of Operand Intensity                                                      | 93  |

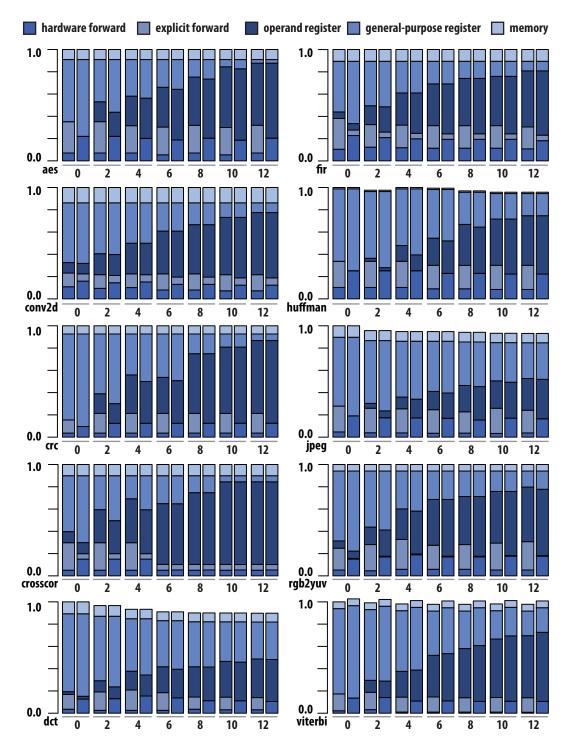

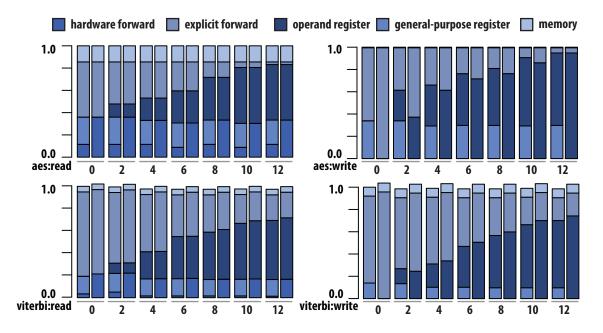

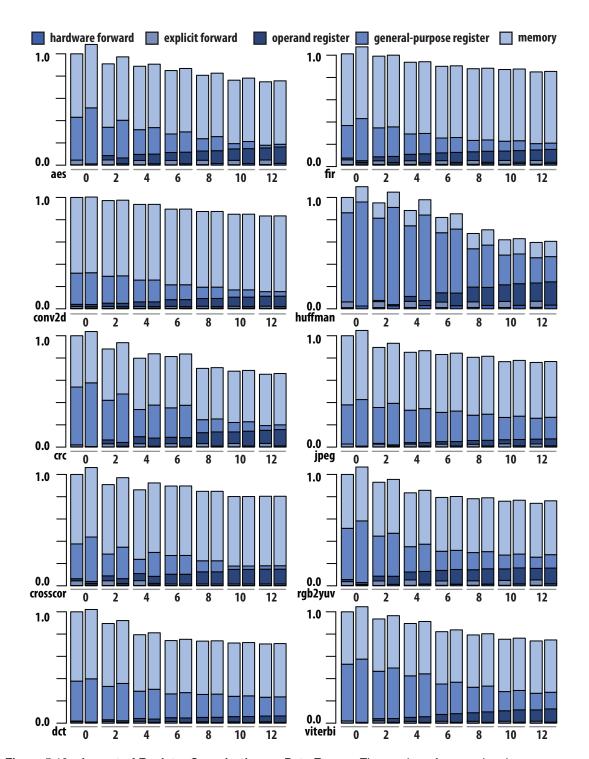

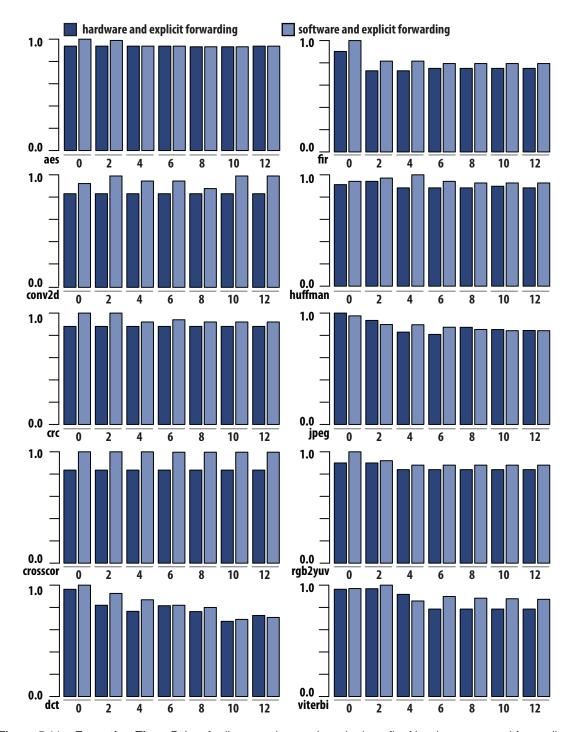

| 5.8  | Impact of Operand Registers on Data Bandwidth                                         | 95  |

| 5.9  | Operand and Result Bandwidth                                                          | 96  |

| 5.10 | Impact of Register Organization on Data Energy                                        | 98  |

| 5.11 | Execution Time                                                                        | 100 |

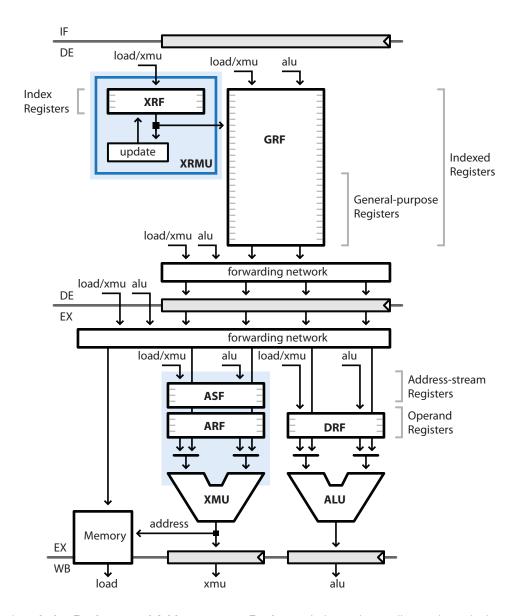

| 6.1  | Index Registers and Address-stream Registers                                          | 107 |

| 6.2  | Finite Impulse Response Filter Kernel                                                 | 114 |

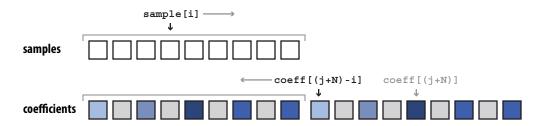

| 6.3  | Finite Impulse Response Filter                                                        | 114 |

| 6.4  | Assembly Fragment Showing Scheduled Inner Loop of FIR Kernel                          | 115 |

| 6.5  | Assembly Fragment Showing use of Index Registers in Inner Loop of fir Kernel          | 116 |

| 6.6  | Assembly Fragment Showing use of Address-stream Registers in Inner Loop of fir Kernel | 116 |

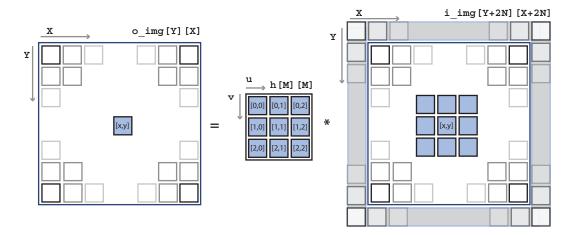

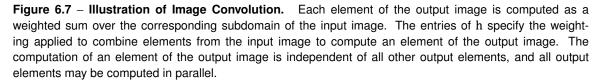

| 6.7  | Illustration of Image Convolution                                                     | 117 |

| 6.8  | Image Convolution Kernel                                                              | 117 |

| 6.9  | Assembly Fragment for Convolution Kernel                                              | 119 |

| 6.10 | Assembly Fragment for Convolution Kernel using Address-Stream Registers               | 119 |

| 6.11 | Convolution Kernel using Indexed Registers                                            | 120 |

| 6.12 | Convolution Kernel using Vector Loads                                                 | 121 |

| 6.13 | Data Reuse in Indexed Registers                                                       | 121 |

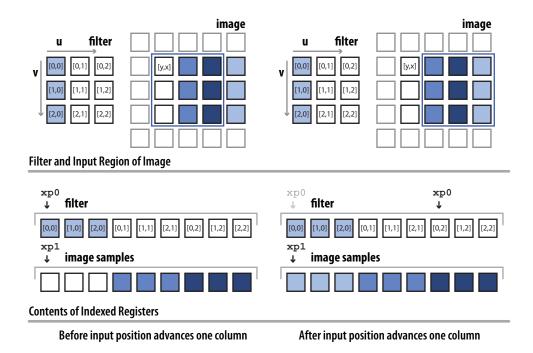

| 6.14 | Static Kernel Code Size                                                               | 122 |

| 6.15 | Dynamic Kernel Instruction Count                                                      | 123 |

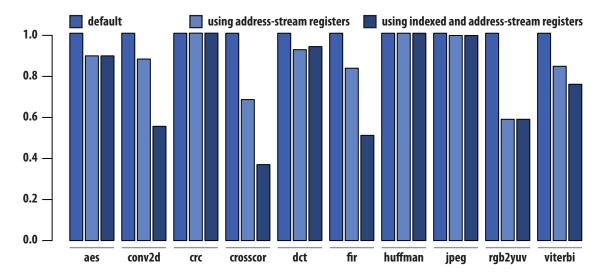

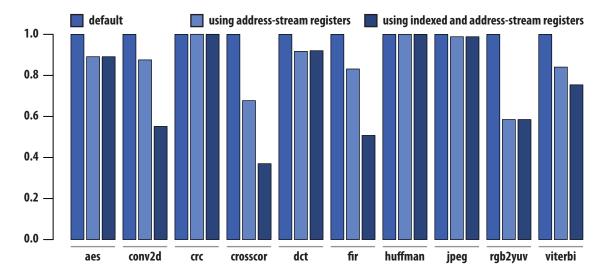

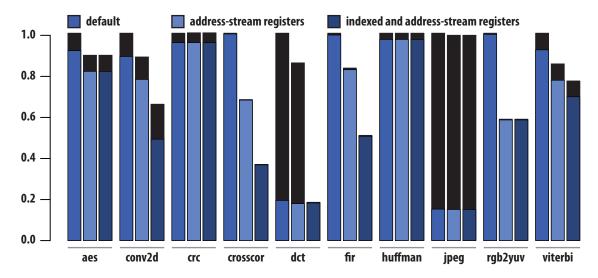

| 6.16 | Normalized Kernel Execution Times                                                     | 125 |

| 6.17 | Normalized Kernel Instruction Energy                               | 26 |

|------|--------------------------------------------------------------------|----|

| 6.18 | Normalized Kernel Data Energy 12                                   | 27 |

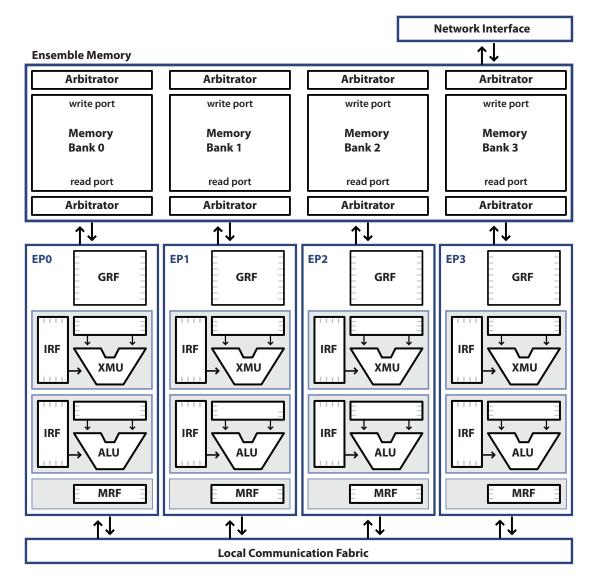

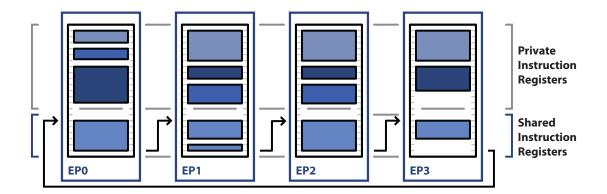

| 7.1  | Ensemble of Processors                                             | 33 |

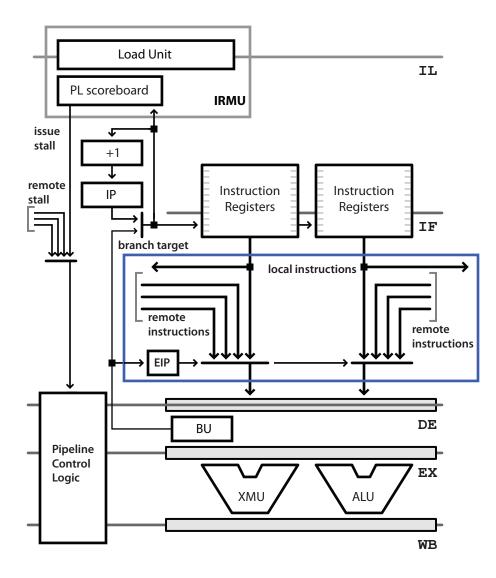

| 7.2  | Group Instruction Issue Microarchitecture                          | ;8 |

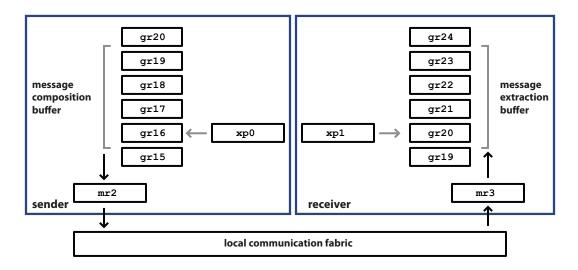

| 7.3  | Composing and Receiving Messages in Indexed Registers              | 10 |

| 7.4  | Source Code Fragment for Parallelized fir                          | 1  |

| 7.5  | Mapping of fir Data, Computation, and Communication to an Ensemble | 12 |

| 7.6  | Assembly Listing of Parallel fir Kernel                            | 12 |

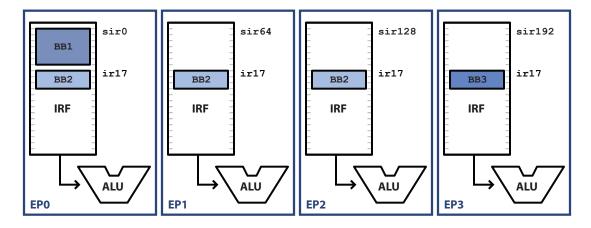

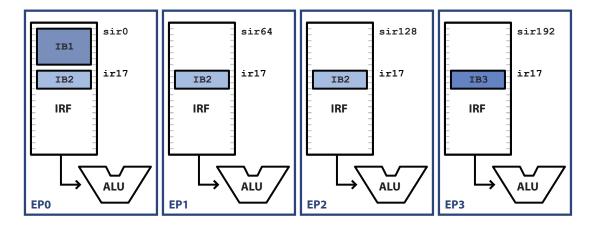

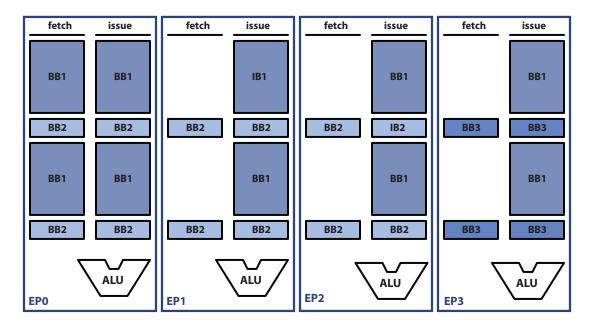

| 7.7  | Mapping of Instruction Blocks to Instruction Registers             | 13 |

| 7.8  | Parallel fir Kernel Instruction Fetch and Issue Schedule           | 4  |

| 7.9  | Shared Instruction Register Allocation                             | 15 |

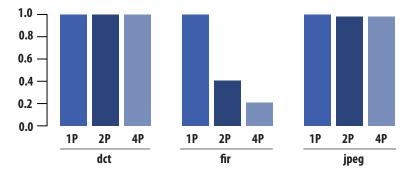

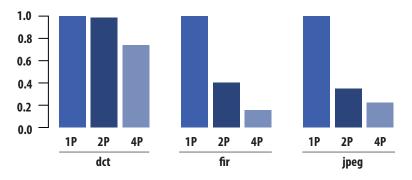

| 7.10 | Normalized Latency of Parallelized Kernels                         | 6  |

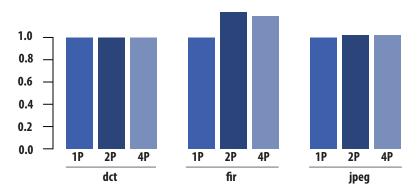

| 7.11 | Normalized Throughput of Parallelized Kernels                      | 17 |

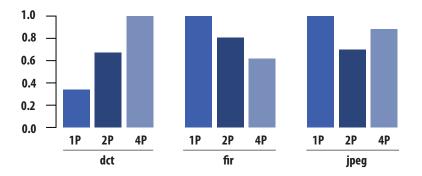

| 7.12 | Aggregate Instruction Energy                                       | 8  |

| 7.13 | Normalized Instruction Energy                                      | 18 |

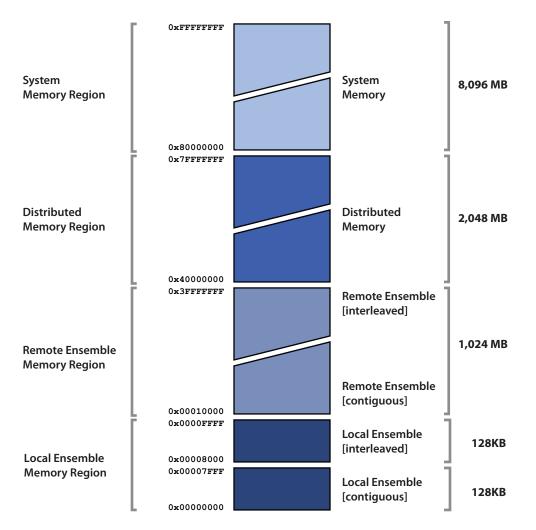

| 8.1  | Elm Memory Hierarchy                                               | 54 |

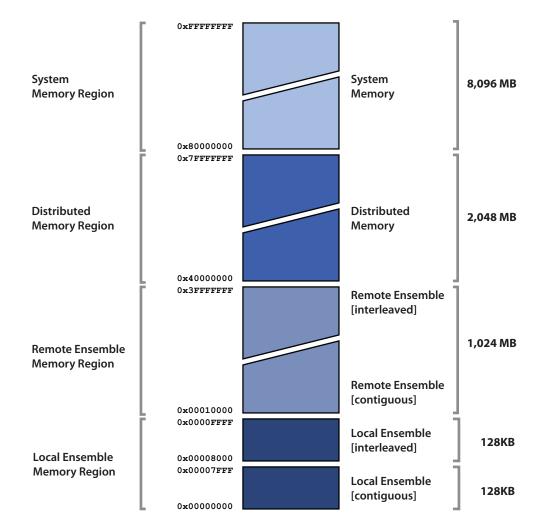

| 8.2  | Elm Address Space                                                  | 56 |

| 8.3  | Flexible Cache Hierarchy                                           | 58 |

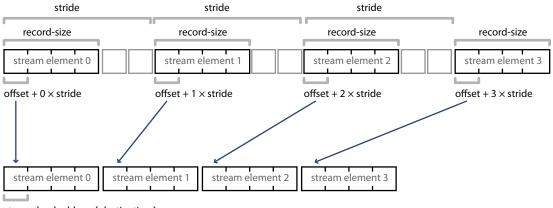

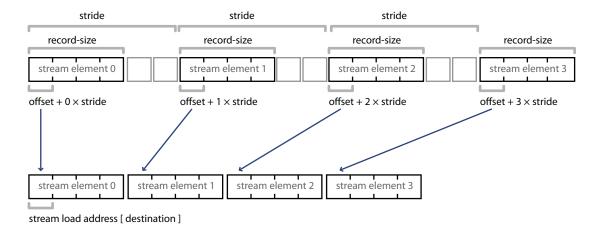

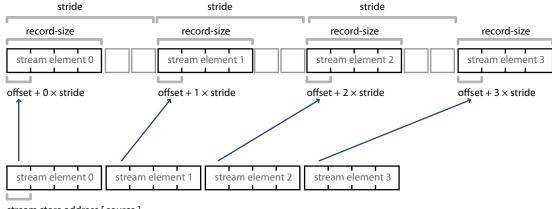

| 8.4  | Stream Load using Non-Unit Stride Addressing 16                    | 50 |

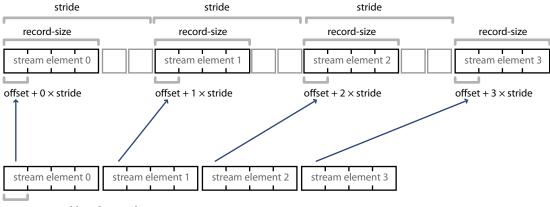

| 8.5  | Stream Store using Non-Unit Stride Addressing 16                   | 50 |

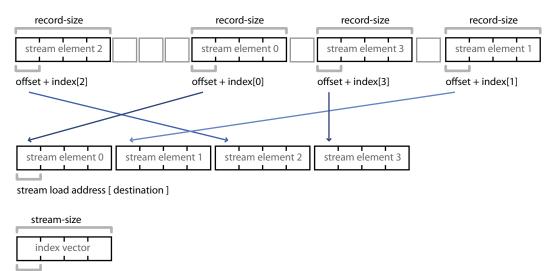

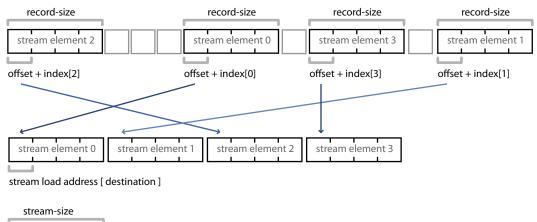

| 8.6  | Stream Load using Indexed Addressing 16                            | 51 |

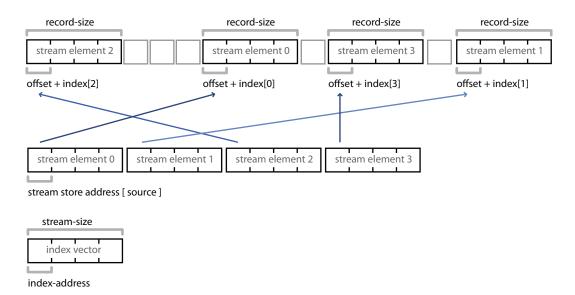

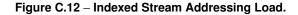

| 8.7  | Stream Store using Indexed Addressing 16                           | 51 |

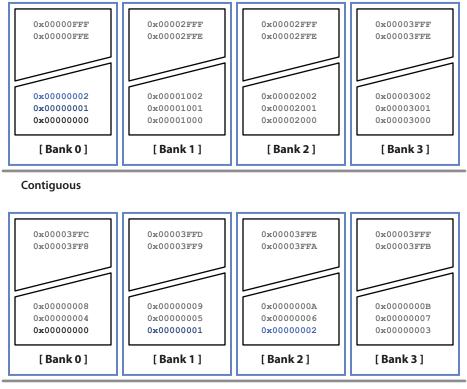

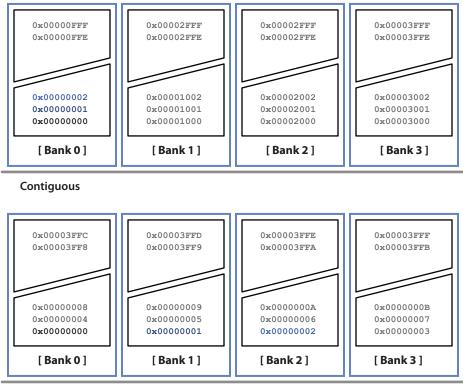

| 8.8  | Local Ensemble Memory Interleaving 16                              | 52 |

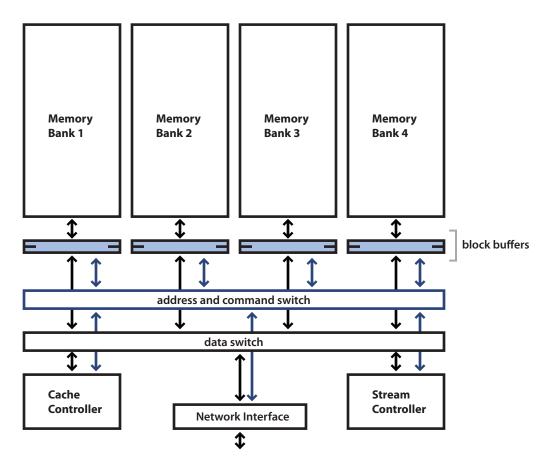

| 8.9  | Memory Tile Architecture                                           | 56 |

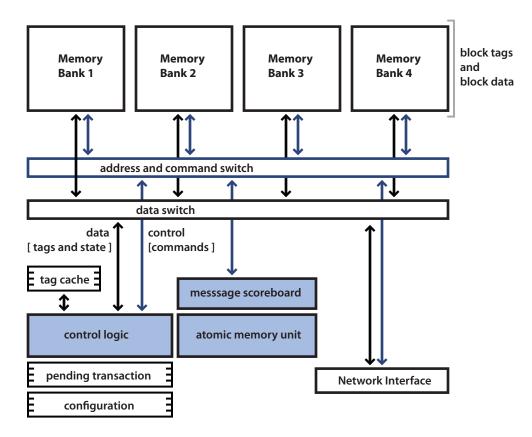

| 8.10 | Cache Architecture                                                 | 58 |

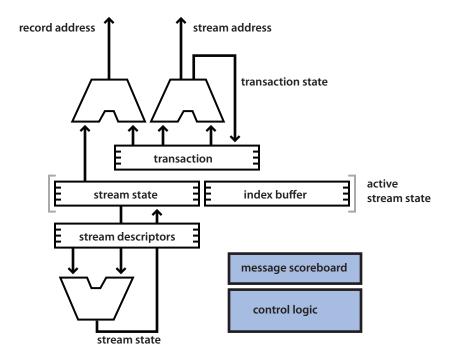

| 8.11 | Stream Architecture                                                | 0  |

| 8.12 | Formats used by <b>read</b> Messages                               | /1 |

| 8.13 | Formats used for write Messages                                    | 12 |

| 8.14 | Formats used for compare-and-swap Messages                         | 12 |

| 8.15 | Formats used by fetch-and-add Messages                             | 12 |

| 8.16 | Formats of <b>copy</b> Messages                                    | 13 |

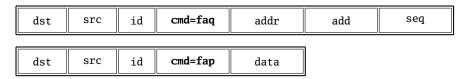

| 8.17 | Formats of <b>read-stream</b> Messages                             | 13 |

| 8.18 | Formats of write-stream messages                                   | 14 |

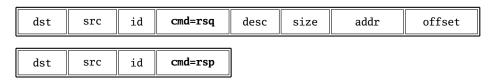

| 8.19 | Formats of <b>read-cache</b> messages                              | 14 |

|      | Formats of write-cache messages 17                                 | 15 |

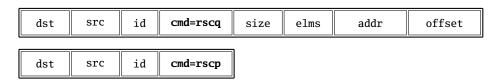

|      | Formats of <b>read-stream-cache</b> messages                       | 15 |

| 8.22 | Formats of write-stream-cache messages                             | /6 |

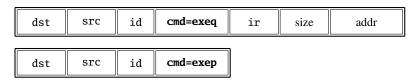

| 8.23 | Format of <b>execute</b> Command Messages                          | /6 |

| 8.24                                                             | Format of <b>dispatch</b> Command Messages                             | 177                                                                                                                             |

|------------------------------------------------------------------|------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|

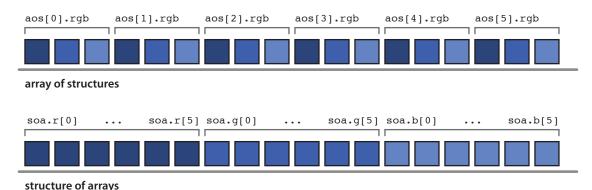

| 8.25                                                             | Examples of Array-of-Structures and Structure-of-Arrays Data Types     | 177                                                                                                                             |

| 8.26                                                             | Scalar Conversion Between Array-of-Structures and Structure-of-Arrays  | 178                                                                                                                             |

| 8.27                                                             | Stream Conversion Between Array-of-Structures and Structures-of-Arrays | 178                                                                                                                             |

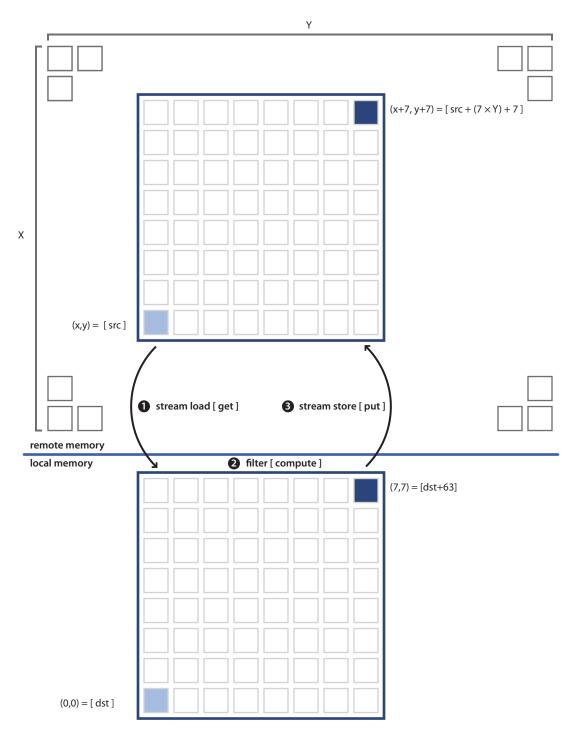

| 8.28                                                             | Image Filter Kernel                                                    | 180                                                                                                                             |

| 8.29                                                             | Implementation using Remote Loads and Stores [Kernel 1]                | 181                                                                                                                             |

| 8.30                                                             | Implementation using Decoupled Remote Loads and Stores [Kernel 2]      | 182                                                                                                                             |

| 8.31                                                             | Implementation using Block Gets and Puts [Kernel 3]                    | 182                                                                                                                             |

| 8.32                                                             | Implementation using Decoupled Block Gets and Puts [Kernel 4]          | 183                                                                                                                             |

| 8.33                                                             | Implementation using Stream Loads and Stores [Kernel 5]                | 184                                                                                                                             |

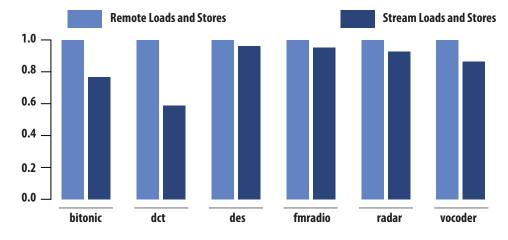

| 8.34                                                             | Normalized Kernel Execution Times                                      | 185                                                                                                                             |

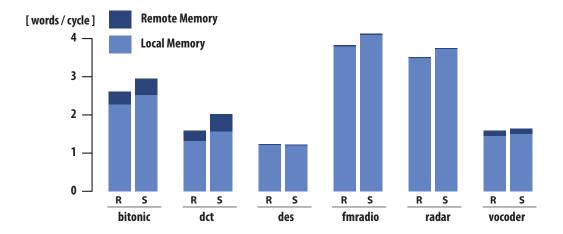

| 8.35                                                             | Memory Bandwidth Demand                                                | 186                                                                                                                             |

| 8.36                                                             | Normalized Memory Access Breakdown                                     | 186                                                                                                                             |

| 8.37                                                             | Normalized Memory Messages                                             | 187                                                                                                                             |

| 8.38                                                             | Normalized Memory Message Data                                         | 188                                                                                                                             |

| <b>C</b> 1                                                       |                                                                        | 207                                                                                                                             |

| C.1                                                              | $\mathcal{C}$ $\mathbf{I}$                                             | 207                                                                                                                             |

| C.2                                                              | e                                                                      | 208                                                                                                                             |

| C.3                                                              | Forwarding Registers                                                   | 210                                                                                                                             |

| C.4                                                              |                                                                        |                                                                                                                                 |

|                                                                  | 5                                                                      | 214                                                                                                                             |

| C.5                                                              | Address-stream Register Format                                         | 214<br>214                                                                                                                      |

| C.6                                                              | Address-stream Register Format                                         | 214<br>214<br>221                                                                                                               |

| C.6<br>C.7                                                       | Address-stream Register Format                                         | 214<br>214<br>221<br>221                                                                                                        |

| C.6<br>C.7<br>C.8                                                | Address-stream Register Format                                         | 214<br>214<br>221<br>221<br>223                                                                                                 |

| C.6<br>C.7<br>C.8<br>C.9                                         | Address-stream Register Format                                         | <ul> <li>214</li> <li>214</li> <li>221</li> <li>221</li> <li>223</li> <li>224</li> </ul>                                        |

| C.6<br>C.7<br>C.8<br>C.9<br>C.10                                 | Address-stream Register Format                                         | <ul> <li>214</li> <li>214</li> <li>221</li> <li>221</li> <li>223</li> <li>224</li> <li>229</li> </ul>                           |

| C.6<br>C.7<br>C.8<br>C.9<br>C.10<br>C.11                         | Address-stream Register Format                                         | <ul> <li>214</li> <li>214</li> <li>221</li> <li>221</li> <li>223</li> <li>224</li> <li>229</li> <li>229</li> </ul>              |

| C.6<br>C.7<br>C.8<br>C.9<br>C.10<br>C.11<br>C.12                 | Address-stream Register Format                                         | <ul> <li>214</li> <li>214</li> <li>221</li> <li>223</li> <li>224</li> <li>229</li> <li>229</li> <li>230</li> </ul>              |

| C.6<br>C.7<br>C.8<br>C.9<br>C.10<br>C.11<br>C.12<br>C.13         | Address-stream Register Format                                         | <ul> <li>214</li> <li>214</li> <li>221</li> <li>223</li> <li>224</li> <li>229</li> <li>229</li> <li>230</li> <li>230</li> </ul> |

| C.6<br>C.7<br>C.8<br>C.9<br>C.10<br>C.11<br>C.12<br>C.13<br>C.14 | Address-stream Register Format                                         | <ul> <li>214</li> <li>214</li> <li>221</li> <li>223</li> <li>224</li> <li>229</li> <li>229</li> <li>230</li> </ul>              |

# **Chapter 1**

## Introduction

Embedded computer systems are everywhere. Most of my contemporaries at Stanford carry mobile phone handsets that are more powerful than the computer I compiled my first program on. Embedded applications are adopting more sophisticated algorithms, evolving into more complex systems, and covering broader application areas as increasing performance and efficiency allow new and innovative technologies to be implemented in embedded systems.

Embedded applications will eventually exceed general-purpose computing in prevalence and importance. I argue that efficient programmable embedded systems are a critical enabling technology for future embedded applications. Improving the energy efficiency of computer systems is presently one of the most important problems in computer architecture. Perhaps the only other problem of similar importance is easing the construction of efficient parallel programs. As this dissertation demonstrates, data and instruction communication dominates energy consumption in modern computer systems. Consequently, improving efficiency necessarily entails reducing the energy consumed delivering instructions and data to processors and function units.

This dissertation describes Elm, an efficient programmable architecture for embedded applications. A central theme of this dissertation is that the efficiency of programmable embedded systems can be improved significantly by exposing deep and distributed storage hierarchies to software. This allows software to exploit temporal and spatial reuse and locality at multiple levels in applications in order to reduce instruction and data movement. Elm implements a novel distributed and hierarchical system organization that allows software to exploit the abundant parallelism, reuse, and locality that are present in embedded applications. Elm provides a variety of mechanisms to assist software in mapping applications efficiently to massively parallel systems. To improve efficiency, Elm allows software to explicitly schedule and orchestrate the movement of instructions and data.

Although this dissertation mostly contemplates efficiency, the relative complexity of mapping applications to Elm informed many of the architectural decisions. Mapping applications from high level descriptions of systems to detailed implementations imposes substantial engineering and time costs. The Elm architecture attempts to simplify the complex and arduous task of compiling and mapping software that must satisfy real-time performance constraints to programmable architectures. Elm is designed to allow applications to be

compiled from high-level languages using optimizing compilers and efficient runtime systems, eliminating the need for extensive development in low-level languages. The Elm architectures is specifically designed to allow software to embed strong assertions about dynamic system behavior and to construct deterministic execution and communication schedules.

## **1.1 Embedded Computing**

It has become rather difficult to differentiate clearly between embedded computer systems and generalpurpose computer systems. Embedded systems continue to increase in complexity, scope, and sophistication. Advances in semiconductor and information technology made massive computing capability both inexpensive and pervasive. The following paragraphs describe ways in which embedded applications and embedded computer systems differ significantly from general-purpose computer systems.

**Power and Energy Efficiency** — Embedded systems have demanding power and energy efficiency constraints. Active cooling systems and packages with superior thermal characteristics increase system costs. Many embedded systems operate in harsh environments and cannot be actively cooled. The limited space within enclosures may preclude the use of heat sinks. In mobile devices such as cellular telephone handsets, energy efficiency is a paramount design constraint because devices rely on batteries for energy and must be passively cooled.

**Performance and Predictability** — Contemporary embedded applications have demanding computation requirements. For example, signal processing in a 3G mobile phone handsets requires upwards of 30 GOPS for a 14.4 Mbps channel, while signal processing requirements for a 100 Mbps OFDM [110] channel can exceed 200 GOPS [131]. Future applications will present even more demanding requirements as more so-phisticated communications standards, compression techniques, codecs, and algorithms are developed. In addition, many applications impose real-time performance requirements on embedded computer systems. For example, a digital video decoder must deliver frames to the display at a rate that is consistent with the video stream, as there is little buffering in such systems to decouple decoding from presentation. Control systems, such as those found in automotive and telecommunications applications, impose even more demanding real-time constraints.

Designing systems to satisfy real-time performance constraints is challenging. Designers must reason about the dynamic behavior of complex systems with many interacting hardware and software components. The design process is simplified significantly when hardware and software is constructed to allow reasonably strong assertions to be made about the performance of components perform and how they interact. Predicting the performance of modern processors is notoriously difficult because structures such as caches and branch prediction units that improve performance introduce significant amounts of variability into the execution of software. Embedded processors often provide mechanisms that allow software to eliminate some of the variability, such as caches that allow specific cache blocks and ways to be locked. However, such mechanisms are typically exposed to software in such a way that programmers must program at a very low-level of abstraction. Application-specific fixed-function hardware can often be designed to deliver deterministic behavior that is readily analyzed and understood, though this comes at the expense of designers explicitly specifying the behavior of the hardware in precise detail.

For most embedded applications with real-time constraints, delivering performance and capabilities beyond those required to satisfy the real-time performance requirements offers little benefit. Rather than optimizing for computational performance, the design objective is often to minimize costs and reduce energy consumption.

**Cost and Scalability** — Embedded applications present a broad range of performance needs and cost allowances. Components within a cellular network such as base stations may be expensive because the systems are expected to be deployed for many years. Network operators prefer for these systems to be extensible and upgradeable so that deployed equipment can be updated as new technologies and standards are developed, and operators are accordingly willing to pay a premium for upgradeable systems that preserve their capital investments. Components in edge and client devices such as cellular handsets must be inexpensive as they are typically discarded after a few years.

Cost and energy efficiency considerations favor integrating more components of a system on a single die. Historically, costs associated with fabricating, testing, and packaging chips have been dominant in most embedded systems. The modest non-recurring engineering and tooling costs associated with the design, implementation, verification, and production of mask sets were amortized over the large production volumes needed to meet the demand for the consumer products that account for most embedded systems. Low volume systems, such as those used in defense and medical applications, exhibited different cost structures, and often had considerably greater selling prices.

However, it has become increasingly more difficult and expensive to design, implement, and verify chips in advanced semiconductor processes. Because programmable systems are presently not efficient enough for demanding embedded applications to be implemented in software, many embedded systems require significant amounts of application-specific fixed-function logic to perform computationally demanding tasks. The design of these systems involves the manual partitioning and mapping of applications to many different hardware and software components, and intensive hardware design and validation efforts. The implementation complexity and effort associated with developing application-specific hardware impose significant engineering costs, and the time and effort required to implement and verify application-specific fixed-function logic increases with the scale and complexity of a system. Furthermore, the inflexibility of deployed systems that rely on application-specific fixed-function hardware increases the cost of implementing new standards and slows their adoption because existing infrastructure must be replaced.

The significant cost of designing new systems often discourages the development, adoption, and deployment of innovative applications, technologies, algorithms, protocols, and standards. For example, the expenses associated with developing novel medical equipment can limit the deployment and accessibility of important medical devices, as the potential markets for new devices may not be large enough to adequately amortize development costs in addition to those costs associated with regulatory approval and clinical trials. Because designs require very large volumes to justify such engineering costs, designs will be limited to individual products with large volumes and families of related products with large aggregate volumes.

#### [Chapter 1 – Introduction]

This favors configurable and programmable systems, such as programmable processors, field programmable gate arrays, and systems that integrate fixed-function hardware and programmable processors on a single die. Unfortunately, partitioning applications between software and hardware requires programming at low-levels of abstraction to expose the hardware capabilities to software, which increases application software development costs and development times: the design and verification of a complex system-on-chip can require hundreds of engineer-years [102] and incur non-recurring engineering costs in excess of 20 M - 40 M.

## **1.2 Technology and System Trends**

Billions of dollars in research and development have driven decades of steady improvements in semiconductor technology. These improvements have allowed manufacturers to increase the number of transistors that can be reliably and economically integrated on a single chip. Transistor densities have historically doubled approximately every two years with the introduction of a new CMOS process generation, and densities at present allow billions of transistors to be fabricated reliably on a single die.

Until recently, most computer architecture research focused on techniques for using additional transistors to improve the single-thread performance of existing applications. Processors were designed with deeper pipelines to allow clock frequencies to increase faster than transistor switching speeds improved with scaling, while increasingly more complex and aggressive microarchitectures were used to improve instruction execution rates. Many of the additional transistors were used to implement impressive collections of execution units that allowed increasing numbers of instructions to be in flight and complete out of order. As pipeline depths and relative memory latencies increased, more of the additional transistors were used to implement the larger caches, more complex superscalar issue logic, and more elaborate predictors that were needed to deliver an adequate supply of instructions and data to the ravenous execution units. Fundamental physical constraints and basic economic constrains, such as the cost of building cooling systems to dissipate heat from integrated circuits, limit the ability of these techniques to deliver further improvements in sequential processor performance without continued voltage scaling.

#### **Interconnect and Communication**

Interconnect performance benefits less than transistor performance from scaling. Consequently, improvements in wire performance fail to maintain pace with improvements in transistor performance, and communication becomes relatively more expensive in advanced technologies. Classic linear scaling causes interconnect resistance per unit length to increase while capacitance per unit length remains approximately constant [36]. Because local interconnect lengths decrease with lithographic scaling, classical scaling causes local interconnect capacitances to decrease and resistance to increase such that the characteristic *RC* response time of scaled local wires remains approximately constant. The reduction in capacitance improves energy efficiency and the increase in wire densities delivers greater aggregate bandwidth, but the increase in resistance results in wires that appear slow relative to a scaled transistor. To compensate, the thickness of metal layers has often been scaled at a slower rate to reduce wire resistance [68], and wires in contemporary CMOS processes are often taller than they are wide. However, effects such as carrier surface scattering cause conductance to degrade more rapidly as scaled wires become narrower [67]. Wires that span fixed numbers of transistor gate pitches shrink with lithographic scaling, and the resulting reduction in capacitance compensates for some of the increase in resistance. Though repeater insertion and the use of engineered wires can partially ameliorate the adverse consequences of interconnect scaling[67], scaling effectively renders communication relatively more expensive than computation in advanced technologies. Somewhat worryingly, interconnect conductance decreases significantly when the mean free path becomes comparable to the thickness of a wire.

#### Scaling, Power, and Energy Efficiency

Historically, semiconductor scaling simultaneously improved the performance, density, and energy efficiency of integrated circuits by scaling voltages with lithographic dimensions, commonly referred to as Dennard scaling [36]. Theoretically, Dennard scaling maintains a constant power density while increasing switching speeds deliver faster circuits and increasing transistor densities allow more complex designs to be manufactured economically. Unfortunately, the subthreshold characteristics of devices tend to degrade when threshold voltages are reduced as devices are scaled. The reduction in threshold voltages allows supply voltages to be lowered without degrading device performance, thereby reducing switching power dissipation and energy consumption. However, the reductions in transistor threshold voltages specified for Dennard scaling result in increased subthreshold leakage currents, which effectively limits the extent to which threshold voltages can be usefully reduced. Leakage currents presently contribute a significant fraction of the total energy consumption and power dissipation in modern processes designed for high-performance integrated circuits.

With the performance and efficiency of many contemporary systems limited by power dissipation, poor subthreshold characteristics seem likely to prevent further significant threshold voltage scaling [47, 69]. Increasing device variation and mismatch, which results from scaling [115], exacerbates the problem, as it becomes increasingly difficult to control device characteristics such as threshold voltages [117]. Without continued transistor threshold voltage scaling, further supply voltage reductions will reduce device switching speeds, effectively trading reductions in area efficiency for improvements in energy efficiency. High-performance systems are limited by their ability to deliver and dissipate power; many of the future improvements in the performance of these systems will depend on improvements in efficiency, so that computation demands less power. Similarly, mobile and embedded systems are limited by cost, power, and battery capacity. Consequently, energy efficiency has become a paramount design consideration and constraint across all application domains.

## **1.3** A Simple Problem of Productivity and Efficiency

Simple in-order processor cores, such as those used in low-power embedded applications, are more efficient than the complex cores that dominate modern high-performance computer architectures. With less elaborate hardware used to orchestrate the delivery of instructions and data, more of the energy consumed in

#### [Chapter 1 – Introduction]

simple cores is used to perform useful computation. However, merely integrating large numbers of simple conventional cores will not deliver efficiencies that are anywhere near sufficient for demanding embedded applications that currently require application-specific integrated circuits. As data presented in this dissertation demonstrates, most of the energy consumed in microprocessors is used to move instructions and data, not to compute. Consequently, programmable systems deliver poor efficiency relative to dedicated fixed-function hardware. The efficiency of programmable embedded systems is particularly poor compared to fixed-function implementations because the operations used in embedded applications, fixed-point arithmetic and logic operations, are inexpensive compared to delivering instructions and data to the function units: performing a 32-bit fixed-point addition requires less energy than reading its operands from a conventional register file and writing back its result, as Table 1.1 shows. Because interconnect benefits less than logic from improvements in semiconductor technology, the interconnect-dominated memories and buses that deliver instructions and data to the function units consume an increasing fraction of the energy. As discussed previously, this imbalance will not improve with advances in semiconductor technology. Instead, architectures must be designed specifically to reduce communication, capturing more instruction and data bandwidth in simple structures that are close to function units, to deliver improvements in efficiency.

This dissertation focuses mostly on technologies for improving efficiency. The efficient embedded computing project in which Elm evolved developed technologies that addressed both the problem of programming massively parallel systems and improving system efficiency. Both are challenging and ambitious research problems. The architecture I describe attempts to allow software to construct deterministic execution schedules to simplify the arduous task of compiling parallel software to meet real-time performance constraints.

## **1.4 Collaboration and Previous Publications**

This dissertation describes work that was performed as part of an effort by members of the Concurrent VLSI Architecture research group within the Stanford Computer Systems Laboratory to develop architecture, compiler, and circuit technologies for efficient embedded computer systems [12, 13, 19, 33]. Jongsoo Park was responsible for the implementation and maintenance of the compilers we developed as part of the project. The benchmarks that appear in this dissertation were written and maintained by Jongsoo Park, David Black-Shaffer, Vishal Parikh, and myself.

## **1.5 Dissertation Contributions**

This dissertation makes the following contributions.

Efficiency Analysis of Embedded Processors — This dissertation presented an analysis of the energy efficiency of a contemporary embedded RISC processor, and argued that inefficiencies inherent in conventional RISC architectures will prevent them from delivering the efficiencies demanded by contemporary and emerging embedded applications.

| Datapath Operations                            |           | Relativ       | e Energy |

|------------------------------------------------|-----------|---------------|----------|

| 32-bit addition                                | 520 fJ    | $1 \times$    |          |

| 16-bit multiply                                | 2,200 fJ  | $4.2 \times$  |          |

| 32-bit pipeline register                       | 330 fJ    | $0.63 \times$ | I        |

| Embedded RISC Processor                        |           | Relativ       | e Energy |

| Register File [ 32 entries 2R+1W ]             |           |               |          |

| 32-bit read                                    | 250 fJ    | $0.48 \times$ | I        |

| 32-bit write                                   | 470 fJ    | 0.90 	imes    |          |

| Data Cache [ 2 KB 4-way set associative ]      |           |               |          |

| 32-bit load                                    | 3,540 fJ  | 6.8 	imes     |          |

| 32-bit store                                   | 3,530 fJ  | $6.8 \times$  |          |

| miss                                           | 1,410 fJ  | $2.7 \times$  | -        |

| Instruction Cache [2 KB 4-way set associativ   | /e ]      |               |          |

| 32-bit fetch                                   | 3,500 fJ  | $6.8 \times$  |          |

| miss                                           | 1,410 fJ  | $2.7 \times$  |          |

| 128-bit refill                                 | 9,710 fJ  | $19 \times$   |          |

| Instruction Filter Cache [ 64-entry direct-map | pped ]    |               |          |

| 32-bit fetch                                   | 990 fJ    | $1.9 \times$  |          |

| miss                                           | 430 fJ    | $0.82 \times$ |          |

| 128-bit refill                                 | 2,560 fJ  | $4.9 \times$  |          |

| Instruction Filter Cache [ 64-entry fully-asso | ciative ] |               |          |

| 32-bit fetch                                   | 1,320 fJ  | $2.5 \times$  |          |

| miss                                           | 980 fJ    | $1.9 \times$  |          |

| 128-bit refill                                 | 2,610 fJ  | 5.0 	imes     |          |

| Execute add Instruction [ Lower Bound ]        | 5,320 fJ  | $10.2 \times$ |          |

**Table 1.1** – **Estimates of Energy Expended Performing Common Operations.** The data were derived from circuits implemented in a 45 nm CMOS process that is tailored for low standby-power applications. The process uses thick gate oxides to reduce leakage, and a nominal supply of 1.1 V to provide adequate drive current. The energy used to execute an add instruction includes fetching an instruction, reading two operands from the register file, performing the addition, writing a pipeline register, and writing the result to the register file.

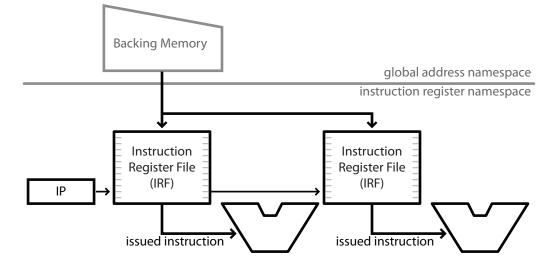

**Instruction Registers** — This dissertation introduced the concept of instruction registers. Instruction registers are implemented as efficient small register files that are located close to function units to improve the efficiency at which instructions are delivered.

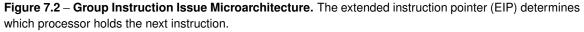

**Operand Registers** — This dissertation described an efficient register organization that exposes distributed collections of operand registers to capture instruction-level producer-consumer locality at the inputs of function units. This organization exposes the distribution of registers to software, and allows software to orchestrate the movement of operands among function units.

**Explicit Operand Forwarding** — This dissertation described the use of explicit operand forwarding to improve the efficiency at which ephemeral operands are delivered to function units. Explicit operand forwarding uses the registers at the outputs of function units to deliver ephemeral data, which avoids the costs associated with mapping ephemeral data to entries in the register files.

**Indexed Registers** — This dissertation presented a register organization that exposes mechanisms for accessing registers indirectly through indexed registers. The organization allows software to capture reuse and locality in registers when data access patterns are well structured, which improves the efficiency at which data are delivered to function units.

Address Stream Registers — This dissertation presented a register organization that exposes hardware for computing structured address streams as address stream registers. Address stream registers improve efficiency by eliminating address computations from the instruction stream, and improve performance by allowing address computations to proceed in parallel with the execution of independent operations.

The Elm Ensemble Organization — This dissertation presented an Ensemble organization that allows software to use collections of coupled processors to exploit data-level and task-level parallelism efficiently. The Ensemble organization supports the concept of processor corps, collections of processors that execute a common instruction stream. This allows processors to pool their instruction registers, and thereby increase the aggregate register capacity that is available to the corps. The instruction register organization improves the effectiveness of the processor corps concept by allowing software to control the placement of shared and private instructions throughout the Ensemble.

This dissertation presented a detailed evaluation of the efficiency of distributing a common instruction stream to multiple processors. The central insight of the evaluation is that the energy expended transporting operations to multiple function units can exceed the energy expended accessing efficient local instruction stores. In exchange, the additional instruction capacity may allowing additional instruction working sets to be captured in the first level of the instruction delivery hierarchy. Consequently, the improvements in efficiency depend on the characteristics of the instruction working set. Elm allows software to exploit structured datalevel parallelism when profitable by reducing the expense of forming and dissolving processor corps.

The Elm Memory System — This dissertation presented a memory system that distributes memory throughout the system to capture locality and exploit extensive parallelism within the memory system. The memory system provides distributed memories that may be configured to operate as hardware-managed caches or software-managed memory. This dissertation also described how simple mechanisms provided by the hardware allow the cache organization to be configured by software, which allows a virtual cache hierarchy to be adjusted to capture the sharing and reuse exhibited by different applications. The memory system exposes mechanisms that allow software to orchestrate the movement of data and instructions throughout the memory system. This dissertation described mechanisms that are integrated with the distributed memories to improve the handling of structured data movement within the memory system.

## **1.6 Dissertation Organization**

Before proceeding it seems prudent to sketch an outline of the remainder of this dissertation. Chapter 2 presents an analysis of contemporary embedded architectures and argues that conventional architectures will not provide the efficiencies demanded by contemporary and emerging embedded applications. Chapter 3

introduces the Elm architecture, and presents the central unifying themes and ideas of the dissertation. Chapters 4 through 6 describe aspects of the Elm processor architecture that improve the efficiency at which instructions and operands are delivered to function units. Chapter 7 describes how collections of processors are assembled into Ensembles, and discusses various issues related to using collections of processors to exploit data-level and task-level parallelism. Chapter 8 describes the Elm memory system. Chapter 9 concludes the dissertation, summarizing contributions and suggesting future research directions.

Three appendices provide additional materials that would interrupt the flow of the thesis were they presented within the dissertation proper. Appendix A describes the experimental methodology and simulators that were used to obtain the data presented throughout this dissertation. Appendix B describes the kernel and benchmark codes that are discussed throughout the dissertation and are used to evaluate various ideas and mechanisms. Appendix C provides a listing of instructions that are somewhat unique to Elm and a detailed description of the Elm instruction set architecture. The reader may find these useful when contemplating various assembly code listings that appear in this dissertation.

# **Chapter 2**

## **Contemporary Embedded Architectures**

Contemporary embedded computer systems comprise diverse collections of electronic components. Advances in semiconductor scaling allow complex systems to be integrated one a single system-on-chip. Most system-on-chip components comprise heterogeneous collections of microprocessors, digital signal processors, application-specific fixed-function hardware accelerators, memory controllers, and input-output interfaces that allow the chip to communicate with other devices. In most contemporary embedded systems, the majority of the computation capability is provided by a few system-on-chip components.

It is reasonable to wonder whether we could replace the fixed-function hardware with collections of simple processors similar to the RISC processors that are prevalent in contemporary embedded systems. The processors would perhaps be organized as a multicore or manycore processor system-on-chip. It is possible for such an architecture to deliver sufficient arithmetic bandwidth to satisfy the demands of most applications, as a tiled collection of small processors can provide a large aggregate number of function units. However, I argue in this chapter that the energy efficiency of simple RISC processors is insufficient for such a system to deliver acceptable power and energy efficiency.

This chapter provides a brief examination of existing embedded computer systems. We begin with a case study of a simple and efficient embedded RISC processor that is representative of contemporary commercial processors; we consider its efficiency, and examine where and how energy is expended. We then discuss strategies and technologies that have been proposed for improving energy efficiency. We conclude with a survey of a few relevant architectures that have used these technologies to improve efficiency.

## 2.1 The Efficiency Impediments of Programmable Systems

Analyzing how area and energy is consumed in simple RISC processors provides significant insight into the efficiency limitations of conventional programmable processors. Table 2.1 lists significant attributes of a very simple embedded processor. The processor is derived from a synthesizable implementation of 32-bit SPARC processor designed for embedded applications [51]. We modified the design to remove everything except the integer pipeline, instruction and data caches, and those parts of the memory controller that are needed to

| Instruction Set Architecture | SPARC V8 [32-bit]                                           |

|------------------------------|-------------------------------------------------------------|

| Clock Frequency              | 500 MHz                                                     |

| Pipeline                     | 7 Stage Integer Pipeline                                    |

| Hardware Multiplier          | 16-bit $\times$ 16-bit with 40-bit Multiply-Accumulate Unit |

| Register Windows             | 2 windows                                                   |

| Register File                | 40  registers  [2R + 1W]                                    |

| Instruction Cache            | 4 KB Direct-Mapped                                          |

| Data Cache                   | 4 KB Direct-Mapped                                          |

|                              |                                                             |

**Table 2.1** – **Embedded RISC Processor Information.** The processor is based on a synthesizable 32-bit SPARC core. The processor contains an integer pipeline, data and instruction cache controllers, and a basic memory controller interface. Many of the applications we consider in this dissertation operate on 16-bit operations. The integer unit provides a 16-bit hardware multiplier, which is adequate for most operations, and implements 32-bit multiplication instructions as multi-cycle operations.

fetch instructions and data on cache misses. With the hardware needed to support sophisticated architectural features such as virtual memory removed, what remains is a design that approximates an efficient minimal embedded RISC processor. We further modified the implementation to support local clock gating throughout the processor.

#### Area Efficiency

Figure 2.1 shows the area occupied by the processor. The entire design occupies a region that is about 0.5 mm by 0.3 mm. The area reported is measured after the design is placed and routed. As the data presented in the figure clearly illustrate, despite the relative simplicity of the architecture and implementation, the processor area is dominated by circuits that are used to stage instructions and data. The integer core contributes 22.5% of the area, the register file 11.0%, and the instruction and data caches contribute the remaining 66.6%. About 53% of the standard cell area in the integer core is contributed by flip-flops and latches, most of which are used to coordinate the movement of instructions to the function units and to stage operands and results. The tag and data arrays are implemented as high-density SRAM modules that are compiled and provided by the foundry. Despite the density and small capacities of the arrays, the area of the caches is dominated by the tag and data arrays, which consume 56.3% of the entire area. The cache and memory controllers occupy about 15.4% of the cache area.

To evaluate the area efficiency, we need to account for the rate at which the processor completes application work. The number of instructions executed per cycle (IPC) provides a reasonable estimate of the effective processor utilization, though it does not account for how efficiently application operations may be mapped to the processor operations exposed by the instruction set. Figure 2.2 shows the average number of instructions executed per cycle for several common embedded kernels. The kernels are described in detail in Appendix A. The reported data were measured after the persistent instruction and data working sets are captured in the caches; any loss of performance due to cache misses is introduced by compulsory data misses. The processor has a peak instruction execution rate of one instruction per cycle, and the kernels [Chapter 2-Contemporary Embedded Architectures ]

**Figure 2.1** – **Embedded RISC Processor Area.** The area reported is measured after the design is placed and routed. The design occupies a region that is about 0.5 mm by 0.3 mm.

are carefully coded and optimized to reduce the number of avoidable pipeline hazards and stalls. However, compulsory data cache misses, branch delay penalties, and true data dependencies result in the processor sustaining between 65% and 84% of peak instruction throughput.

## **Energy Efficiency**

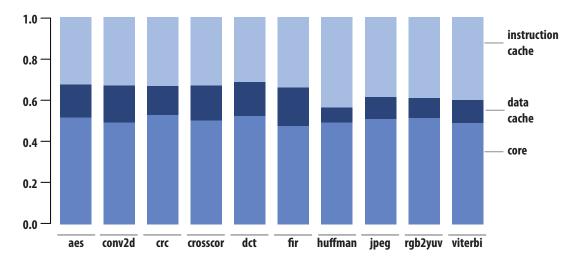

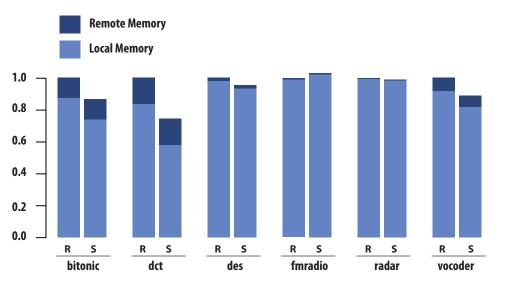

In order to assess the energy efficiency of the processor, we need to understand where energy is expended and the contribution of different operations to the energy consumption. We first consider the relative contribution of the processor core and caches to the aggregate energy consumption. Figure 2.3 shows the distribution of energy consumed in the caches and processor core. The data have been normalized within each kernel to

#### [Section 2.1 – The Efficiency Impediments of Programmable Systems]

**Figure 2.3** – **Energy Consumption by Module for an Embedded RISC Processor.** The cache components include the cache data and tag memory arrays and the cache controllers. The core component includes the integer pipeline and all other control logic. Both components include energy consumed in the clock tree, with energy consumed within shared levels apportioned relative to the clock load within each module.

illustrate clearly the contribution of each component. As the figure illustrates, the composition of the energy consumption is somewhat insensitive to the computation performed by a kernel. The cache energies include both the energy consumed in the storage arrays and the cache controllers. Though the instruction and data caches are similar in structure and identical in capacity, the data cache is more expensive to access because the data cache controller implements additional hardware to support stores and must track which cache blocks have been modified. However, the instruction cache consumes more energy because it is accessed more often. The amount of energy consumed in the processor core is similar to the energy consumed in the caches. This results in part from the small 4 KB caches used in the evaluation.

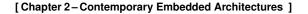

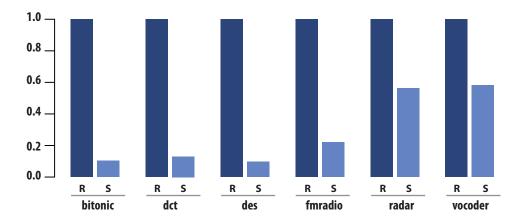

The composition of the dynamic instruction streams provides some insight into the relative contribution of different operations to the energy expended by the processor. It also explains the differences in the relative contributions of the caches. Figure 2.4 shows the frequency of different instruction types in the dynamic instruction streams comprising the kernel executions. The control component corresponds to instructions that affect control flow, such as jumps and conditional branches. The memory component corresponds to instructions that transfer data between registers and memory, such as load and store instructions. The arithmetic and logic component corresponds to compute instructions that operate on data stored in registers.

As Figure 2.4 illustrates, the kernels are dominated by compute and memory instructions. Arithmetic and logic instructions alone account for approximately 70% of the instructions that are executed across the kernels. The small contribution of control instructions results from the compiler aggressively unrolling loops with predictable loop bounds. The notable exceptions are the **huffman** and **jpeg** kernels, both of which contain significant loops with data-dependent iteration counts and data-dependent conditional branches.

The distribution of instruction types provides an incomplete measure for assessing the energy efficiency

**Figure 2.4** – **Distribution of Instructions by Operation Type in Embedded Kernels.** The control component includes control flow instructions, the preponderance of which are conditional branches and jump instructions. The memory component includes data transfer instructions that access memory, which are almost exclusively load and store instructions. The arithmetic and logic component includes all arithmetic and logic instructions, which are dominated by integer arithmetic and logic operations. The processor implements a multiply-and-accumulate instruction, which encodes two basic arithmetic operations. The multiply-and-accumulate instruction is used extensively in the arithmetically intensive kernels.

of the processor because it does not account for how different instructions contribute to the computation demanded by the kernels. Many of the arithmetic and logic instructions encode operations that are not fundamental to the kernels, but a consequence of their implementation. For example, arithmetic and logic instructions may appear in instruction sequences that implement control and memory access operations that cannot be encoded directly in the instruction set. Data references and control statements in programming languages often map to sequences of instructions. For example, a compiler may map an effective address calculation to an instruction sequence comprising an arithmetic instruction followed by a load instruction. It is important that we differentiate operations that are fundamental to a computation from computations that are a consequence of the architecture a computation is mapped to.

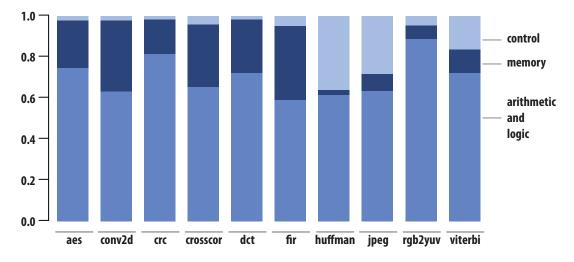

To asses correctly the impact of the processor architecture on its energy efficiency, we implemented a compiler data flow analysis to classify instructions as control and memory operations based on how the values the instructions compute are used rather than the operations instructions perform. The data flow analysis can analyze assembly code listings produced by other compilers. It uses the results of a reaching definitions analysis to propagate data flow information backwards from control flow and memory instructions. The reaching definitions analysis follows variables that are stack allocated and temporarily spilled and restored during a procedure invocation through spills and restores to fixed memory locations. The analysis identifies instructions that compute condition operands to control flow operations and address operands to memory operations. The analysis propagates data flow information backwards through arithmetic and logic instructions to identify sets of dependent arithmetic and logic instructions that compute control and address

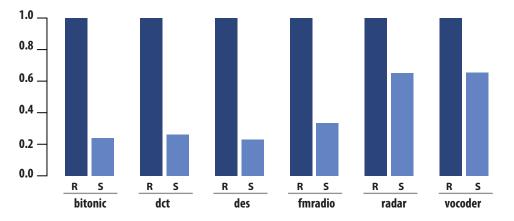

**Figure 2.5** – **Distribution of Instructions within Embedded Kernels.** The control component includes control flow instructions and those arithmetic and logic instructions that compute operands to control flow instructions. The memory component includes data transfer instructions that access memory and those arithmetic and logic instructions that provide address operands to data transfer instructions. The compute component includes arithmetic and logic instructions that implement computations demanded by the kernels. An arithmetic or logic instruction that defines a value that is both fundamental to the computation of a kernel and used by a control or memory operation is designated a compute instruction. An arithmetic or logic instruction that defines a value that compute instruction.

operands. Arithmetic and logic instructions that define values that are used exclusively as condition and address operands or exclusively to compute condition and address operands are classified as control and memory operations.

The results of the analysis appear in Figure 2.5. The data illustrated in the figure provide a more detailed accounting of the composition of the instructions comprising the kernels. Compute operations are encoded in 53% of the instructions on average. The **crosscor** kernel is dominated by memory operations, and only 32% of its instructions encode compute operations. The **rgb2yuv** kernel has very simple control and small data working sets that the compiler maps to the register file, and 77% of its instructions encode compute operations.

To assess the energy efficiency of the processor, we also need to account for the impact of microarchitecture on the energy consumed in the processor core. A significant component of the energy expended in the processors is used to deliver operands to function units and control signals decoded from instructions to data-path control points. Though necessary to execute instructions, such energy is an overhead imposed by the programmability afforded by the architecture.

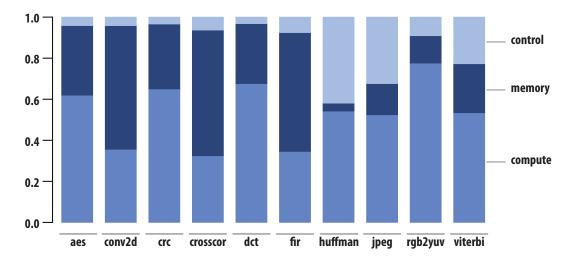

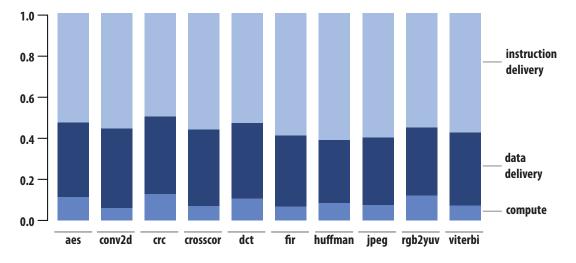

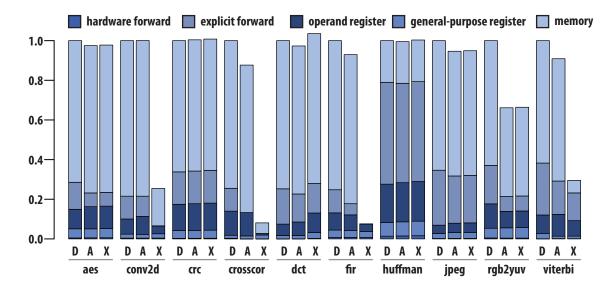

Figure 2.6 shows a detailed analysis of the contribution of instruction delivery, data delivery, and compute to the aggregate energy consumption of each kernel. The instruction delivery energy reflects the preponderance of the energy used to deliver instructions to the data-path control points. Significant components include the energy used to access the instruction cache and transfer instructions to the processor, energy expended

#### [Chapter 2-Contemporary Embedded Architectures ]

**Figure 2.6** – **Distribution of Energy Consumption within Embedded Kernels.** Instruction delivery and data delivery contribute the majority of the aggregate energy consumption for each kernel.

in the instruction fetch and decode logic, and in flip-flops that implement interstage pipeline registers that capture instruction and control signals. The data delivery energy reflects the preponderance of the energy used to transfer data the function units. Significant components include the energy expended accessing the data cache and transferring data between the processor core and data cache, energy expended accessing the register file, driving results back to the register file, and in flip-flops that implement interstage pipeline registers that capture operands and results. The compute component measures the energy used in the function units to complete operations demanded by a kernel. Perhaps the most salient and significant aspect of the data is the small component of the energy contributed by compute, which varies from 6.0% to 12.8%.

Table 2.2 provides the average energy per instruction for each of the kernels. The table lists separately the component of the average energy per instruction that we attribute to instruction delivery, data delivery, and compute for each of the kernels. Differences between the kernels reflects differences in the computations and working sets.

## 2.2 Common Strategies for Improving Efficiency

We can reason about many strategies for improving efficiency as mechanisms that attempt to reduce instruction and data bandwidth demand somewhere in the system. Some attempt to shift more of the bandwidth demand closer to the function units, while others attempt to eliminate instruction and operand references. Often, these schemes are described as exploiting some form of reuse and locality to keep more control and data bandwidth close to the function units. The following are some of the most pervasive and effective techniques.

|             | aes  | conv2d | crc  | crosscor | dct  | fir  | huffman | jpeg  | rgb2yuv | viterbi |

|-------------|------|--------|------|----------|------|------|---------|-------|---------|---------|

| Instruction | 34.9 | 33.2   | 30.3 | 32.2     | 37.7 | 34.0 | 35.4    | 39.9  | 32.8    | 32.5    |

| Data        | 23.9 | 23.0   | 22.8 | 21.2     | 26.1 | 19.8 | 17.7    | 21.85 | 19.5    | 19.9    |

| Compute     | 7.4  | 3.6    | 7.9  | 4.1      | 7.5  | 3.9  | 4.9     | 5.0   | 7.2     | 4.1     |

|             | 66.2 | 59.8   | 61.0 | 57.5     | 71.3 | 57.7 | 58.0    | 66.7  | 59.4    | 56.5    |

| Other       | 5.6  | 7.5    | 5.3  | 6.7      | 13.5 | 6.2  | 8.1     | 21.0  | 11.7    | 12.3    |