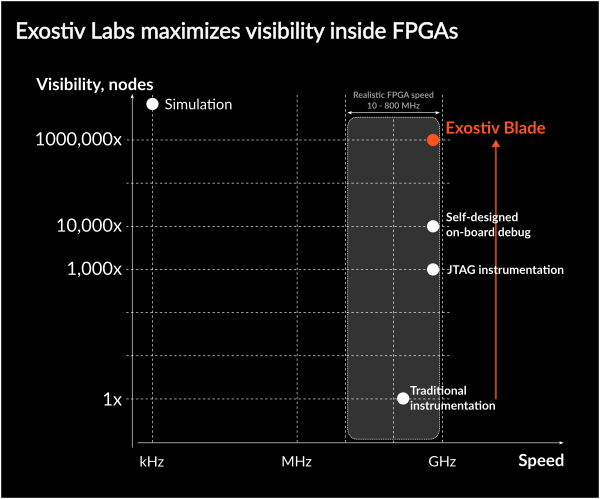

Massive Visibility inside FPGAs

at Operating Speed.

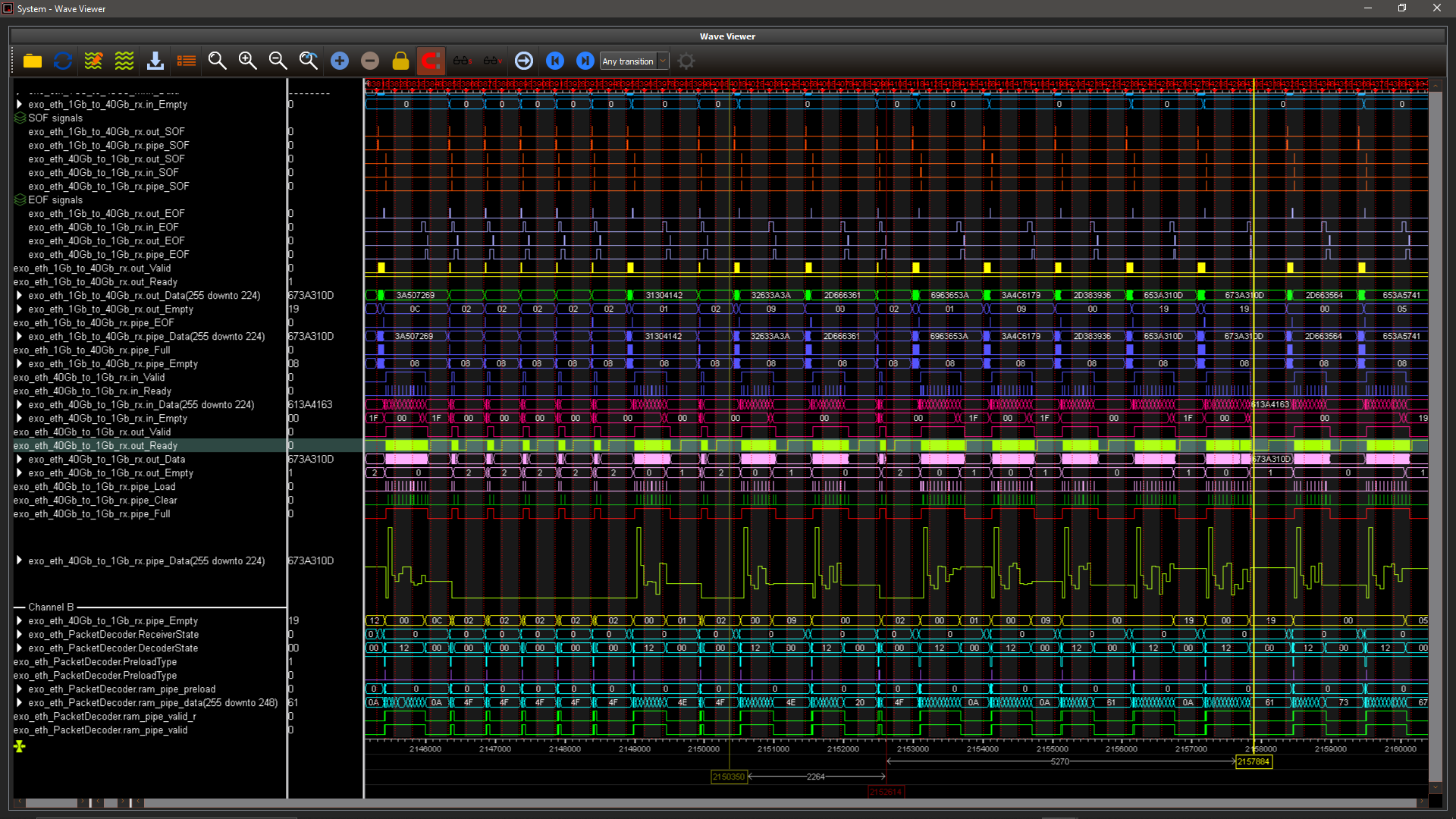

Get clarity for pre-silicon validation and debug.

Visibility is crucial for SoC and FPGA design.

FPGA prototypes play a pivotal role in software design, system validation in realistic environments, regression testing before production and IPs demonstration.

Examining prototypes carefully is essential, as:

-

Bugs emerge from software execution

-

IP assemblies don’t meet performance expectations

-

Simulation assumptions are wrong

-

Systems do not behave well in realistic environments

Data is critical for design and verification iterations.

Our products.

Standard packages are displayed below. Contact us for customized configurations.

Standard and customized packages for all capture needs.

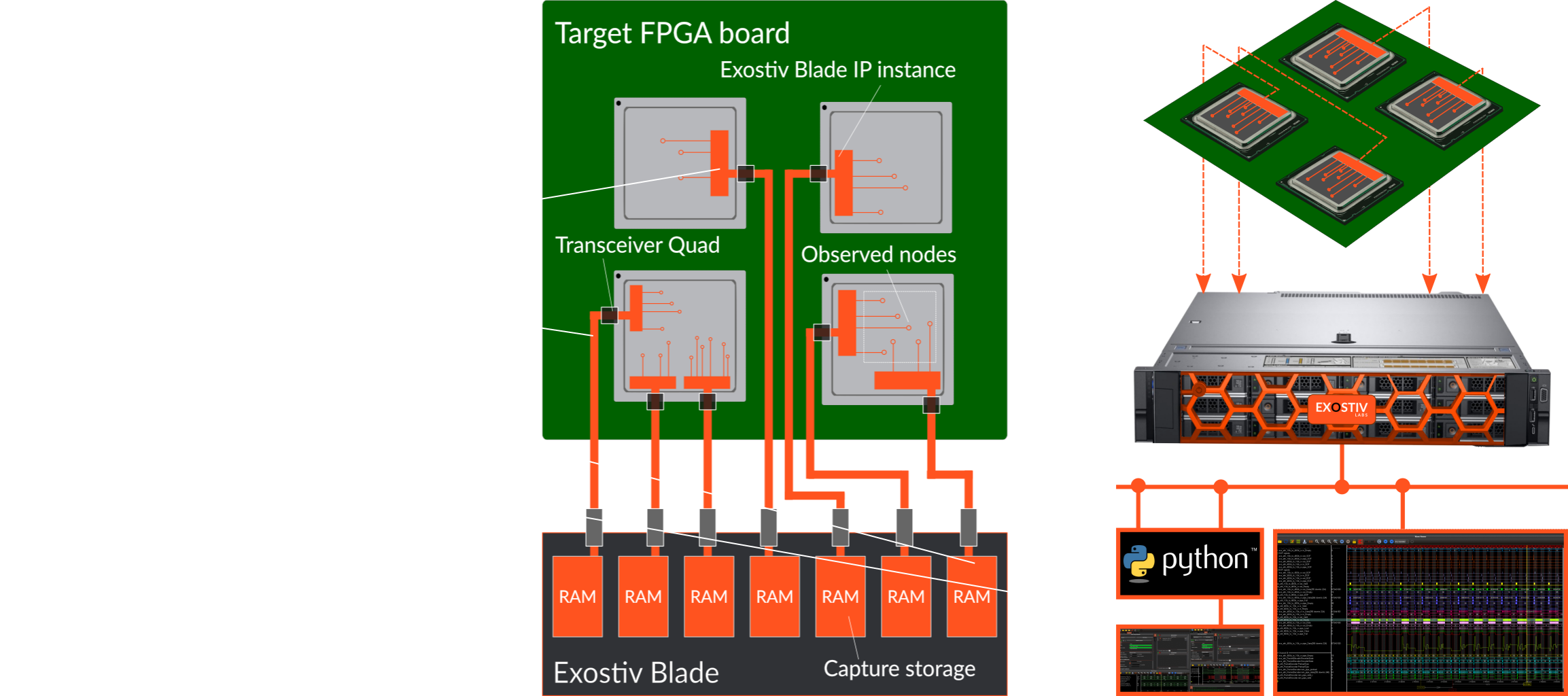

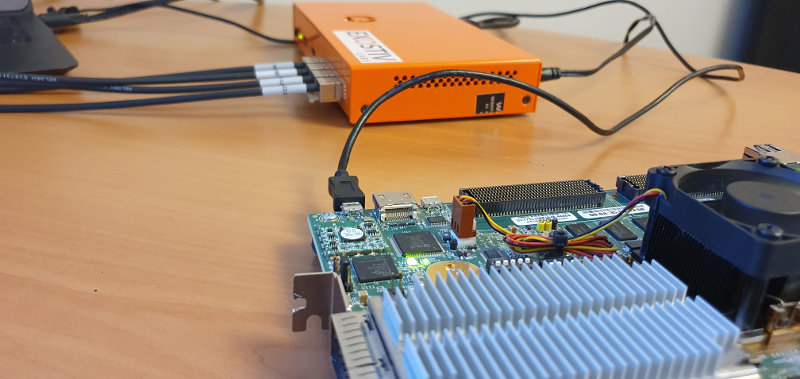

Very deep capture from single or multiple FPGA. At speed.

From benchtop to enterprize-level deployment.

Locally or from remote locations.

|  |  | ||

Exostiv | Exostiv Blade - Compact chassis | Exostiv Blade - Tower chassis | Exostiv Blade - 2U chassis | Exostiv Blade - 4U chassis |

|

|

|

|

|

Latest articles.

Topic : ASIC and SoC Validation | Product presentation & features | Topic : FPGA Prototyping | Webinar - Application case |

10 things you should know before SoC Validation | Exostiv Blade – Managing multiple sites, targets & users | What can Exostiv Blade do for FPGA Prototyping? | Massive Real-time |

Get updates.