SpaceWire IP Core is a VHDL core that implements a complete, reliable and fast SpaceWire encoder-decoder with AXI management interface, synthesizable for FPGA and for reconfigurable SoC Devices.

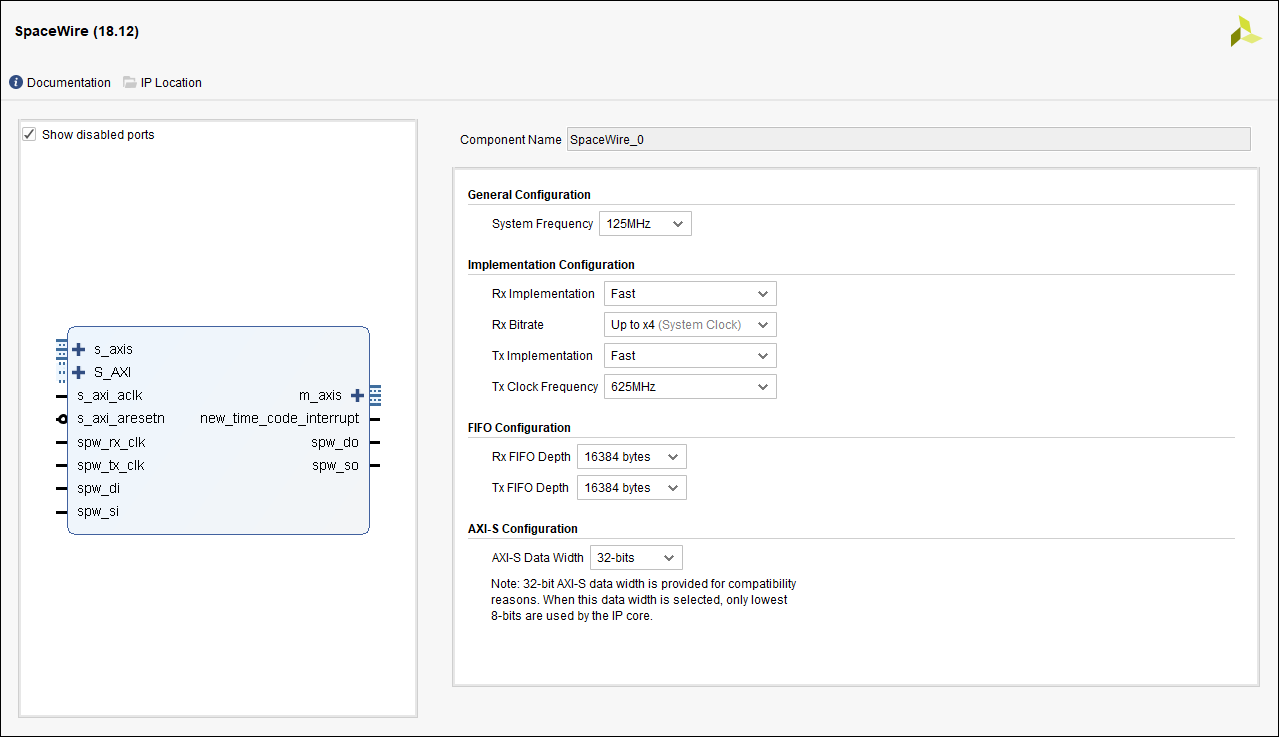

This IP core can operate up to the packet level in point-to-point links, with no “destination address”. It is designed to conform to ECSS-E-ST-50-12C. SpaceWire IP supports two implementation modes, generic and fast, where the transmitter is designed to support bitrates up to 5 times the system clock frequency

SpaceWire IP is supported on the following Xilinx FPGA Families:

- 7-Series (Zynq, Spartan, Artix, Kintex, Virtex)

- Ultrascale (Kintex, Virtex)

- Ultrascale+(Zynq MPSoC, Kintex, Virtex)

- XQR Family (Space Grade FPGA’s): Virtex-5QV and Virtex

SpaceWire IP is designed to be seamless integrated in your FPGA designs by taking advantage of the new Xilinx Vivado Tool, that allows to use the IP Cores in a graphical user interface and configure IP parameters in an easy way.

SpaceWire IP Core key features:

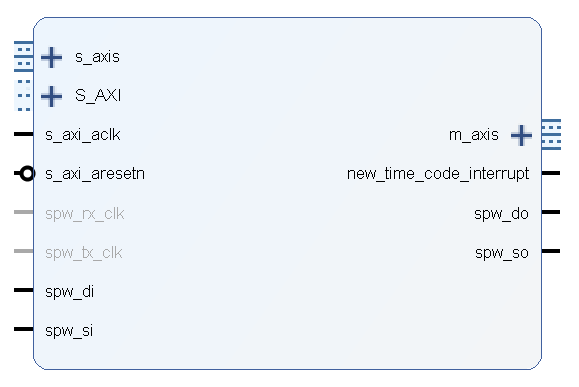

Data interfaces

- Rx Bit-rate up to x4 of the system clock frequency

- Tx Clock Frequency between 100MHz-625MHz

- Separate Clock Domains

FIFO Configuration

- Tx FIFO Depth fully configurable: From 64 bytes to 16384 bytes

- Rx FIFO Depth fully configurable: From 64 bytes to 16384 bytes

Interfaces

- AXI-Stream (Data)

- AXI-4 Lite (Configuration & Management)

Performance

- Up to 200Mbps Link Speed

SpaceWire IP Core can be supported in the SoC-e’s SMARTcia board, a platform designed to be used in space environment, meeting the requirements established by the current regulations.

For more information about this IP, licensing modes and turn-key projects based on this standard: