# mipi<sup>®</sup> DEVCON

Ahmed Ella Mixel Inc. Jeffrey Lukanc Synaptics

Dual Mode MIPI C-PHY<sup>SM</sup>/D-PHY<sup>SM</sup> Use in VR Display IC MIPI ALLIANCE DEVELOPERS CONFERENCE

SEOUL

### Outline

- GPU to Pixel VR Display System

- Mixel C-PHY<sup>SM</sup>/D-PHY<sup>SM</sup> IP in VXR7200

- Summary

© 2018 MIPI Alliance, Inc.

MIPI.ORG/DEVCON | 2018

2

**Synaptics**

# **GPU to Pixel VR Display System**

Synaptics

Mixel, Inc.

© 2018 MIPI Alliance, Inc.

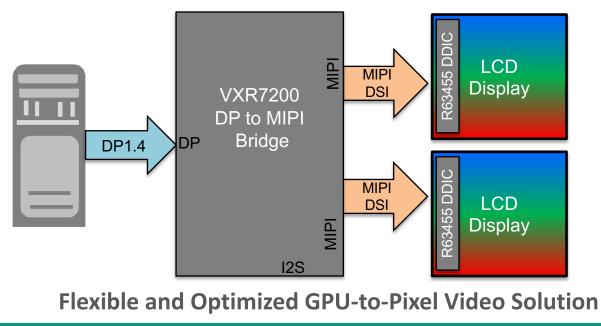

### **GPU to pixel VR display system overview**

Video over DP or USB-C connector from PC or smartphone

MIPI D-PHY or C-PHY interface to displays

MIPI.ORG/DEVCON | 2018

MIPI ALLIANCE DEVELOPERS CONFERENCE 19 OCTOBER 2018 **SEOUL**

#### © 2018 MIPI Alliance, Inc.

# VR Displays Drive Video Interface Technology

- **1.** PPI >1000 eliminates "screen door" effect & enables ability to read text

- Resolution: 2Kx2K minimum, better = 3Kx3K, ideal = 4Kx4K

- 2. Display responsiveness

- For crisp LCD images, need to allocate frame time for pixel settling and backlight flashing

- Additional time required for LCD to settle drives higher DP + MIPI bandwidths

- **3.** VR systems require higher video bandwidths to match display resolutions

- Need 32Gbps raw bandwidth GPU to display

- Need DP DSC support to exceed dual 5.5M pixel displays

- Need MIPI DSC support to exceed 6.2M pixel displays

- Need SPR support for optimized OLED bandwidth

- Foveal transport support allow full resolution foveal images at ½ the DP or MIPI bandwidth

**Synaptics**

Mixel, Inc.

# Synaptics VR Bridge & VR DDIC Chipset Overview

- VR Bridge chip features

- DP1.4 with FEC

- ~1 Line time video latency

- Latency = lag = unresponsive HMD video

- Low latency enables video to match USB Audio

- SST or MST video formats

- Either PC or cellphone applications

- DSC or Synaptics SASPC compression

- Supports 1-4 DDIC per display

- D-PHY<sup>sM</sup> @ 2.5Gbps Tx

- C-PHY<sup>sM</sup> @ 2.5Gsym/sec Tx

- VR DDIC chip features

- Combo C-PHY<sup>SM</sup>/D-PHY<sup>SM</sup> Rx

- DSC or Synaptics SASPC decoders

- Drive up to 4Kx3K displays

- Built-in Foveal Transport image overlay

- FIFO to adjust panel load/scan time

- No need for buffering video in bridge

- Pixel overdrive

- Local dimming

## **VESA & MIPI Display standards interoperability**

### VR Bridge manages both DisplayPort and MIPI sides of bridge

- Provides display requirements to GPU via EDID/DisplayID

- Video formats: Sub-Pixel Render, 420, 444, 8-bit, 10-bit

- Compression: Compression algorithm and settings

- Timing: allocate addition frame time for pixel settle and backlight flashing

- Configures the VR DDIC

- Video formats: Sub-Pixel Render, 420, 444, 8-bit, 10-bit

- Compression: Compression algorithm and settings

- Panel scan time, settle time, backlight flash time

- Pixel overdrive LUT

- Local dimming settings

- FIFO bandwidth settings

#### Mixel, Inc.

**Synaptics**

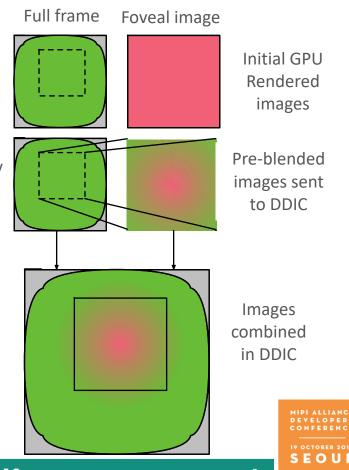

# **Introducing Foveal Transport**

### **Foveal Rendering**

- Renders a foveal image and a low res background image

- Both images are combined and sent at full resolution to a display

- Reduces render time, but benefits are not shared with system!

### **Foveal Transport**

- GPU sends both images to displays *without merging them*

- Gaze point location is embedded in the display data

- DDIC scales full frame and overlays the foveal image

- Chromatic and lens distortion algorithms for each image

- Uses ½ the data and ½ the link bandwidth!

### Why dual-mode C-PHY<sup>SM</sup>/D-PHY<sup>SM</sup> interface is required

- Large legacy display infrastructure requires MIPI D-PHY support for initial bring-up

- MIPI C-PHY required to match DP HBR3 bandwidth and display scan timing

- MIPI DSI-2<sup>SM</sup> & DCS<sup>SM</sup> are compatible with DP 1.4 enabling GPU to display compression

- Foveal Transport is compatible with both DP and MIPI DSI-2

| Parameter                   | No           | 2:1 Compression   | 2:1 Compression | 3:1 Compression | Foveal Transport | 2880x1920 |

|-----------------------------|--------------|-------------------|-----------------|-----------------|------------------|-----------|

|                             | Compression  | Bridge to Display | GPU to Display  | GPU to Display  | GPU to Display   | Display   |

| MIPI data/line (bytes)      | 10,710       | 6,390             | 6,390           | 4,950           | 6,390            | per Eye   |

| MIPI total bandwidth (Gbps) | 15           | 9                 | 9               | 7               | 9                | per Eye   |

| Minimum MIPI C-PHY link:    | 6-trio C-PHY | 4-trio C-PHY      | 4-trio C-PHY    | 3-trio C-PHY    | 4-trio C-PHY     | per Eye   |

| Minimum MIPI D-PHY link:    | None         | 8-lane D-PHY      | 8-lane D-PHY    | 8-lane D-PHY    | 8-lane D-PHY     | per Eye   |

| DP data/line (bytes)        | 17,808       | 17,808            | 8,904           | 5,936           | 8,904            | Host I/F  |

| DP total bandwidth (Gbps)   | 32           | 32                | 16              | 11              | 16               | Host I/F  |

| Minimum DP link:            | 4-lane HBR3  | 4-lane HBR3       | 4-lane HBR2     | 2-lane HBR3     | 2-lane HBR3      | Host I/F  |

### **Reduced MIPI & DP PHY Lane Usage Saves Power**

# Mixel C-PHY<sup>SM</sup>/D-PHY<sup>SM</sup> IP in VXR7200

Mixel, Inc.

**Synaptics**

© 2018 MIPI Alliance, Inc.

MIPI.ORG/DEVCON | 2018

10

MIPI ALLIANCE DEVELOPERS

SEOUL

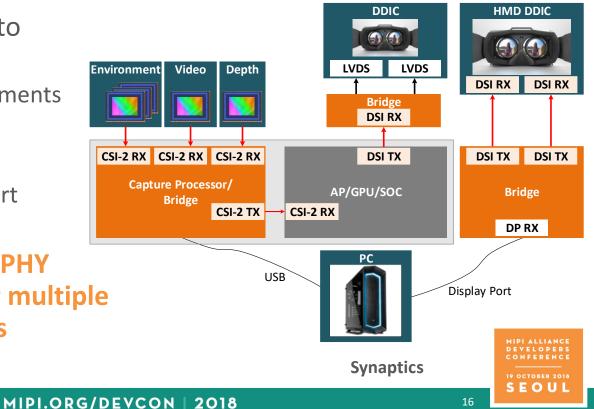

#### DDIC **HMD DDIC XR Generic System Diagram VR** Flavors • LVDS Environment Video LVDS Depth **DSI RX** DSI RX Smartphone Bridge DSI RX Standalone HMD CSI-2 RX CSI-2 RX CSI-2 RX DSI TX DSI TX DSI TX Tethered VR **Capture Processor/** AP/GPU/SOC Bridge Displays Bridge CSI-2 TX CSI-2 RX Immersive DP RX Devices PC – Holographic USB **Display Port Devices** EVELODEE **Synaptics** Mixel, Inc. **19 OCTOBER 2018** SEOUL © 2018 MIPI Alliance, Inc. MIPI.ORG/DEVCON | 2018 11

# **XR System Challenges**

- High Bandwidth Requirements

- High display resolution

- Faster frame rate

- Higher sensor resolution

- High dynamic range

- SOC Design Constraints

- Low Power / Heat

- Package / Minimal pin count

- Minimize die area

- Support multiple use cases

Power and thermal efficiency is essential for XR

# **MIPI Spec Attributes**

- Typical for XR Market

- High bandwidth

- Low power

- Low EMI

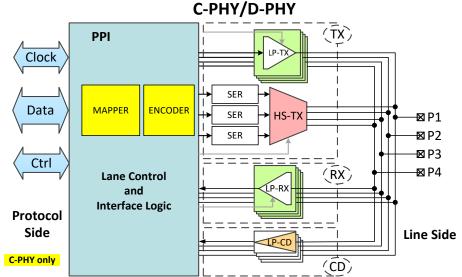

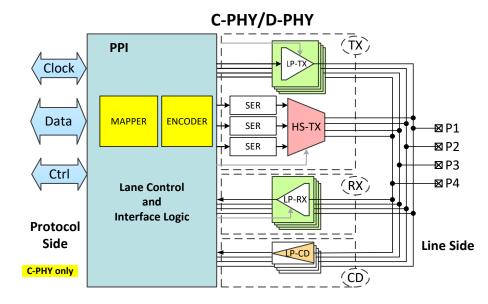

### Mixel C-PHY<sup>SM</sup>/D-PHY<sup>SM</sup> IP integrated in VXR7200

- Dual Mode PHY

- D-PHY v1.2

- C-PHY v1.1

- DSI-2 Controller

- Four Lane in D-PHY mode (10 pins)

- Three Lane in C-PHY mode (9 pins)

- Supports lane swapping and pin swapping features

- Supports de-skew calibration in D-PHY c

- Supports T1 and T2 modes in C-PHY

- BIST with 100% coverage for HM

#### Mixel, Inc.

**Synaptics**

### **MIPI D-PHY<sup>sM</sup> and C-PHY<sup>sM</sup> Comparison**

| Parameter                     | D-PHY v1.2                         | C-PHY v1.1                                     |  |

|-------------------------------|------------------------------------|------------------------------------------------|--|

| Adoption                      | Long history of use, wide adoption | Accelerated adoption, co-<br>exists with D-PHY |  |

| Power/Gbps                    | Efficient                          | Higher efficiency                              |  |

| Maximum Bandwidth<br>@2.5Gsps | 10Gbps for 4 Lanes (10<br>pins)    | 17.1Gbps for 3 Lanes (9<br>pins)               |  |

| Minimum number of pins        | 4                                  | 3                                              |  |

| Flexibility                   | All lanes operate together.        | Each lane can work independently.              |  |

| Mixel, Inc.                   |                                    | Synaptics                                      |  |

| © 2018 MIPI Alliance, Inc.    | MIPI.ORG/DEVCON   2018             | 14                                             |  |

### Advantage of Mixel Dual PHY MIPI C-PHY<sup>SM</sup>/D-PHY<sup>SM</sup>

- Sharing of the serial interface pins

- All D-PHY blocks are re-used for the C-PHY to minimize overhead

- Combo PHY provides the flexibility to support both PHY's using same pins with minimal overhead, while enhancing PPA

**Synaptics**

### **C-PHY<sup>sm</sup>/D-PHY<sup>sm</sup> flexibility in XR System Considerations**

- System Designers need to consider

- Total resolution requirements

- Application targeted

- Number of ports

- Number of lanes per port

- Rate per lane

### The flexibility of C-PHY/D-PHY makes it ideal solution for multiple applications and use-cases

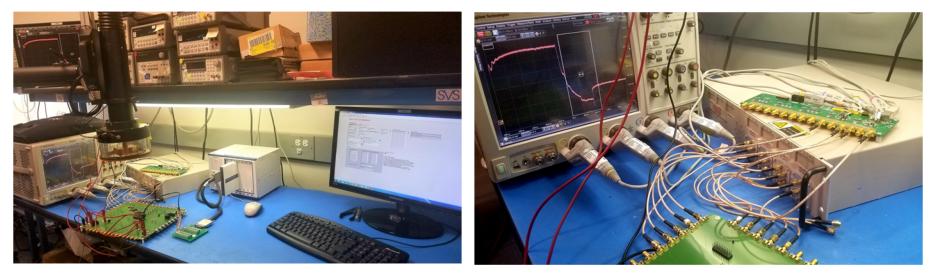

### Silicon Results of VXR7200 MIPI Interfaces

### Test Bench Setups

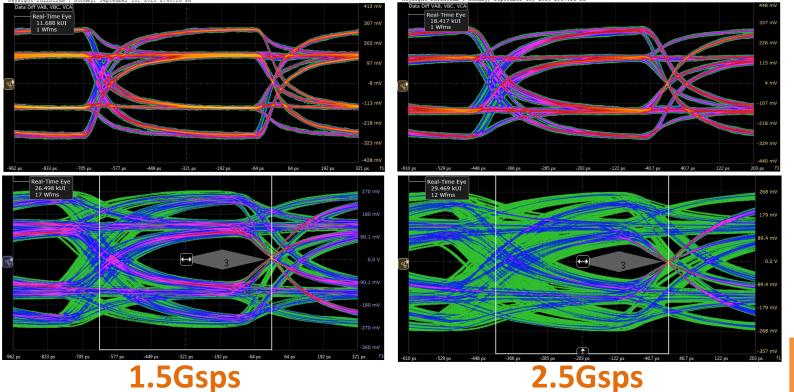

### Silicon Results of VXR7200 C-PHY<sup>SM</sup> Interface

© 2018 MIPI Alliance, Inc.

MIPI.ORG/DEVCON | 2018

18

MIPI ALLIANCE

SEOUL

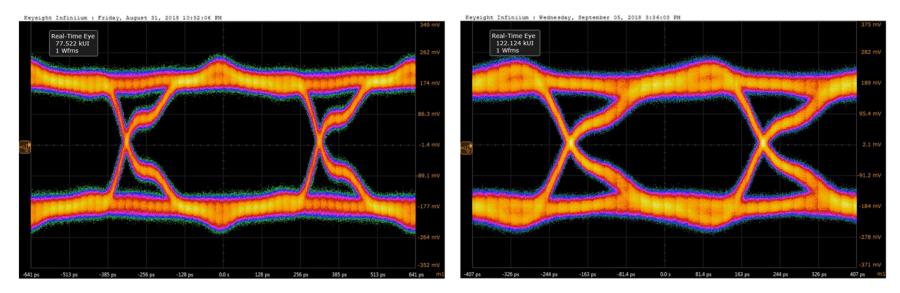

### Silicon Results of VXR7200 D-PHY<sup>sm</sup> Interface

1.5Gbps

# Mixel's IP MIPI solution in XR

- C-PHY<sup>SM</sup>/D-PHY<sup>SM</sup> Combo<sub>a</sub>

- D-PHY<sup>sm</sup> v1.1

- D-PHY<sup>sm</sup> v1.2

- CSI-2<sup>SM</sup>

- DSISM

- DSI-2<sup>SM</sup>

Mixel, Inc.

© 2018 MIPI Alliance, Inc.

### Summary

- Combo C-PHY<sup>SM</sup>/D-PHY<sup>SM</sup> offers a flexible and versatile solution for both system bring-up and application usage

- Mixel's C-PHY/D-PHY link speed makes it ideal for most display applications

- The Combo IP has been integrated into many end products by tier-one SOC, Display and Sensor vendors, several in XR applications

- Mixel's C-PHY/D-PHY are available in multiple configurations and Silicon proven in multiple nodes and foundries

- Synaptics achieved first time silicon success integrating Mixel's C-PHY/D-PHY into VXR7200

MIPI.ORG/DEVCON 2018

**Synaptics**

**Synaptics**

Mixel, Inc.

© 2018 MIPI Alliance, Inc.

### **ADDITIONAL RESOURCES**

Demystifying MIPI C-PHY / D-PHY Subsystem - Tradeoffs, Challenges, and Adoption

https://www.chipestimate.com/Demystifying-MIPI-C-PHY--DPHY-Subsystem-Tradeoffs-Challenges-and-Adoption-/Mixel/Technical-Article/2018/04/24

<u>Synaptics' New Virtual Reality Display Driver and VR Bridge</u> <u>Provide Ultimate User Experience for Emerging Head-Mounted</u> <u>Displays</u>

https://globenewswire.com/news-release/2018/08/28/1557502/0/en/Synaptics-New-Virtual-Reality-Display-Driver-and-VR-Bridge-Provide-Ultimate-User-Experience-for-Emerging-Head-Mounted-Displays.html

### Synaptics chip paves the way for dual 2K VR headsets with 1,000 PPI

https://venturebeat.com/2018/08/28/synaptics-chip-paves-the-way-for-dual-2k-vr-headsets-with-1000-ppi/

### MIPI DevCon 2016: Implementing MIPI C-PHY

https://www.slideshare.net/MIPI-Alliance/mipi-devcon-2016-implementing-mipi-cphy

Mixel, Inc.

**Synaptics**

© 2018 MIPI Alliance, Inc.

# mipi DEVCON THANK YOU

#### MIPI ALLIANCE DEVELOPERS CONFERENCE

SEOUL