Description and Features

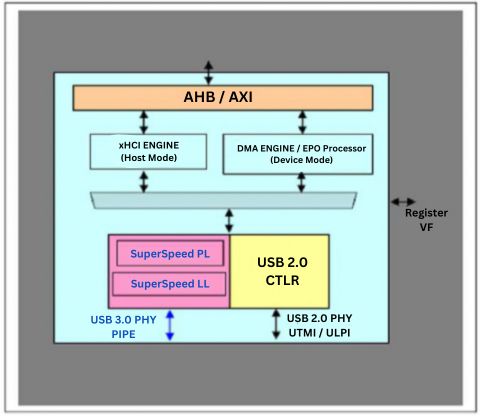

USB 3.0 Dual Mode Controller IP Core uses a high performance DMA engine based on the xHCI specification and presenting either an AHB or AXI interface, this controller offers host and device capabilities. With a very simple application interface that can be easily adapted to standard on-chip-bus interfaces like AXI, AHB, and OCP as well as other standard off-chip interconnects, the Dual Mode Controller core is carefully partitioned to support standard power management schemes, including extensive clock gating and multiple power wells for aggressive power savings. This makes it easy to be integrated in a wide range of applications.

Features

-

Host functionality is compliant with xHCI Rev1.0

-

Compliant with USB3.0 Specification Rev1.0

-

Compliant with USB Specification Rev 2.0

-

Compliant with USB2 Link Power Management

-

Supports Aggressive Low Power Management

-

Configurable core frequency: 125, 250, 500 Mhz.

-

Configurable PIPE Interface for USB3.0 PHY: 8,16, 32 bit.

-

Configurable USB2 PHY Interface : 8/16 bit UTMI,8-biot ULPI interface

-

Optional DMA engine for device mode functionality.

-

Optional endpoint zero processor block for processing standard requests for device mode functionality

-

Flexible User Application Logic

-

Can be adapted by any SoC / OCB interface / offchip interconnects – such as AHB, AXI, PCIe

-

Configurable Datawidth: 32, 64, 128 bit

-

Optional native packet interface

-

Simple Register Interface for internal Register

-

Access – AHB Slave or GDA PBUS Interface

-

Pin or register bit to select between host/device

Benefits

-

Highly modular and configurable design

-

Layered architecture

-

Fully synchronous design

-

Support for both sync and async reset

-

Clearly demarcated clock domains

-

Extensive clock gating support

-

Multiple power well support

-

Software control for key features

Applications

-

Scanners

-

Digital cameras

-

Removable media drives

-

Mass storage devices

-

Display and docking applications

-

Cloud computing

-

Automotive applications

-

Consumer applications

Deliverables

-

Customizable RTL Implementation

-

HDL-based Test Environment with Behavioral Models

-

Test Case Suite

-

Protocol Compliance Checkers, Bus Monitors, and Performance Analyzers

-

Configurable Synthesis Framework

-

Design Handbook

-

Verification Guide

-

Synthesis Manual

-

FPGA Validation Platform for Pre-Tape-out Testing

-

Reference Firmware Implementation and Documentation

![]()