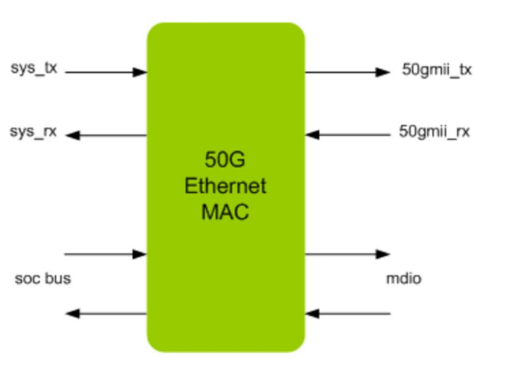

Ethernet 50G MAC core is compliant with IEEE Standard 802.3.2018 Ethernet specification. Through its Ethernet compatibility, it provides a simple interface to a wide range of low-cost devices. Ethernet 50G MAC IP is proven in FPGA environment. It can also support a variety of host bus interfaces for easy adoption into any design architecture - AHB, AHB-Lite, APB, AXI, AXI-Lite, Tilelink, OCP, VCI, Avalon, PLB, Wishbone or custom buses.

Benefits

Exclusive licensing tailored for businesses operating from one location, optimizing access.

Adaptable licensing solution for companies with operations across various sites, promoting widespread utilization.

Enables integration of the IP Core into a solitary FPGA bitstream and ASIC, ensuring focused application.

Provides boundless access to the IP Core for integration into countless FPGA bitstreams and ASIC designs, stimulating endless innovation and adaptability.

Deliverables

Executing the Verilog RTL design in practical application

Validation scripts seamlessly incorporating waivers to cover Linting, CDC analysis, and Synthesis

Comprehensive and detailed reports providing extensive insights into Linting, CDC analysis, and Synthesis methodologies

Utilizing IP-XACT RDL to effectively generate an address map

Consolidating firmware code and Linux drivers into a unified and integrated package

Exhaustive technical documentation comprehensively covering all facets and aspects

Verilog Test Environment with intuitively integrated and seamless test cases