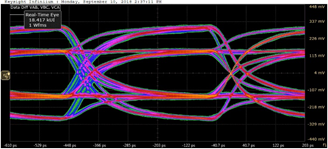

Mixel MIPI D-PHY at 2.5Gbps

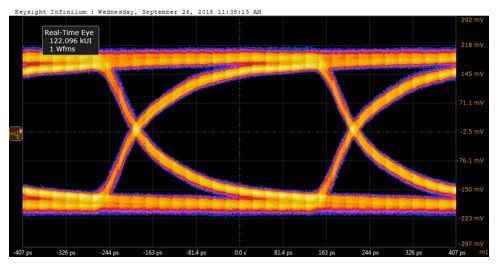

Mixel MIPI C-PHY at 2.5Gsps

MIPI FPGA Platform

Mixel offers a MIPI FPGA Platform that supports Mixel MIPI PHY using our test chips. This enables our IP customers to quickly bring up their MIPI platform, add their own RTL and software, and verify their system performance in record time.

Additionally, we have commercialized our C/D-PHY combo IP by producing a test chip that is now available for not only our IP customers, but also test equipment manufacturers that need to build test equipment targeting the Camera and Display testing markets.

The Mixel C-PHY/D-PHY Test Chip, CD-PHY X153_V1, is a test chip that contains a high-frequency low-power, low-cost, source synchronous, Physical Layer compliant with the MIPI Alliance Standard for D-PHY and C-PHY. The IP can be configured as a MIPI Master or Slave, supporting camera interface CSI-2 v1.2 and display interface DSI v1.3 applications in the D-PHY mode. It also supports camera interface CSI-2 v1.3 and display interface DSI-2 v1.0 applications in the C-PHY mode.

The High-Speed signals have a low voltage swing, while Low-Power signals have large swing. High-Speed functions are used for High-Speed Data traffic while low power functions are mostly used for control.

The Mixel C-PHY/D-PHY test chip consists of CPHY-DPHY universal IP (MXL-CPHY-DPHY-UNIV) with a Clock Lane Module, four Data Lane Modules for D-PHY mode, and three Data Lane Modules for C-PHY mode. In addition to the universal lanes, the IP includes a calibrator module for calibration of termination resistance. Each of these PHY Lane Modules communicates through a differential line to a complementary PHY at the other side of the lane interconnect. MXL-CPHY-DPHY-UNIV is partitioned into a Digital Module – CIL (Control and Interface Logic) and a Mixed Signal Module.

The CIL module interfaces with the Protocol and determines the global operation of the Lane Module.

Mixel’s C-PHY/D-PHY Test Chip consists of Dual mode PHY supporting:

- MIPI C-PHYSM and MIPI D-PHYSM

- Complies with MIPI D-PHY Standard v1.2 and C-PHY Standard v1.0

- Test Chip consists of 1 Clock lane and 4 Data lanes in D-PHY mode

- Test Chip consists of 3 Data lanes in C-PHY mode and PLL and bias circuitry

- Supports both high speed and low-power modes

- 80 Mbps to 2.5Gbps data rate in high-speed mode

- 10 Mbps data rate in low-power mode

- Low power dissipation

- Deskew calibration support in D-PHY

- Loopback testability support

To learn more about Mixel’s silicon-proven IP and test chips, please visit Mixel’s contact page or read Mixel C/D-PHY related whitepapers here.