Description and Features

A SoC or ASIC's USB 4.0 component may be verified ingeniously with the help of the USB 4.0 Verification IP. The USB 4.0 Verification IP complies exactly with USB Specification 4.0 requirements. The USB 4.0 VIP is easily adaptable and may be modified for a variety of particular system applications. SystemVerilog, VMM, RVM, AVM, OVM, UVM, Verilog, SystemC, VERA, Specman E, and non-standard verification environments all natively support USB 4.0 Verification IP. The Smart Visual Protocol Debugger (Smart ViPDebug), a GUI-based debugger that speeds up debugging, is an optional component of the USB 4.0 Verification IP.

Features

-

Compliant with USB4.0 Specification

-

Supports USB4.0 Gen2 and Gen3 Operation

-

Supports constrained randomization of protocol attributes

-

Supports all types of error injection and detection

-

Supports error injection in all the layers of USB 4.0

-

Supports Dual Lane

-

Supports Lane margining and Lane de-skew buffer

-

Supports Side band channels

-

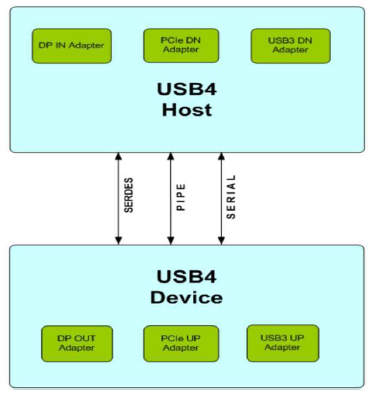

Supports SERIAL, PIPE and SERDES Interface

-

Configurable PIPE Interface width 8, 16 or 32 bits

-

Configurable SERDES Interface width 32, 40, 64 and 80 bits

-

Supports Enumeration process to enumerate hub/device

-

Supports 64/66B Encoding and Decoding for Gen2

-

Supports 128/132B Encoding and Decoding for Gen3

-

Supports Scrambler and Descrambler

-

Supports RS-Forward Error Correction (FEC)

-

Supports Clock compensation

-

Supports Spread spectrum clocking

-

Supports jitter

-

Supports Side band register space

-

Supports Configuration register space

-

Supports Lane adapter, Protocol adapter and Control adapter operations

-

Supports Lane initialization process

-

Supports Low power state

-

Supports Lane bonding mechanism

-

Supports Error detection and Recovery mechanism

-

Supports USB4 Link Equalization TxFFE handshake.

-

Supports all the Side Band Channel transactions

-

Supports Sleep and Wake mechanism with respect to the tunneled protocols

-

Supports Hot plug detection and Disconnect detection

-

Supports SKIP Insertion and Removal

-

Supports Time Sync Notification Ordered Set (TSNOS)

-

Supports following Protocol tunneling, • USB3 tunneling • Display port tunneling • PCIE tunneling

-

Supports all the Transport layer packets

-

Supports HEC, ECC and CRC

-

Supports Path Setup & Path Tear-Down mechanism

-

Supports all the Control packets

-

Supports all the Notification events

-

Supports Time Synchronization

Deliverables

-

Complete regression suite containing all the USB 4.0 testcases.

-

Examples showing how to connect various components, and usage of BFM and Monitor.

-

Detailed documentation of all class, task and function's used in verification env.

-

Documentation also contains User's Guide and Release notes.

![]()