Description and Features

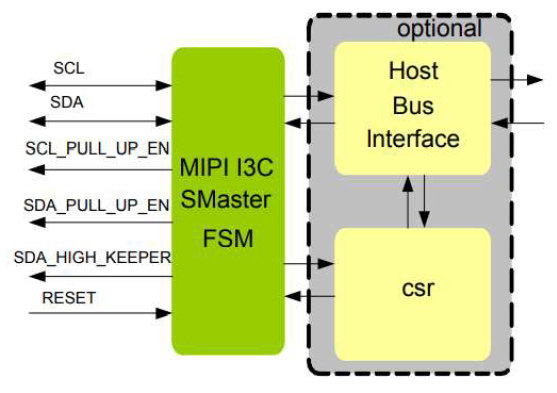

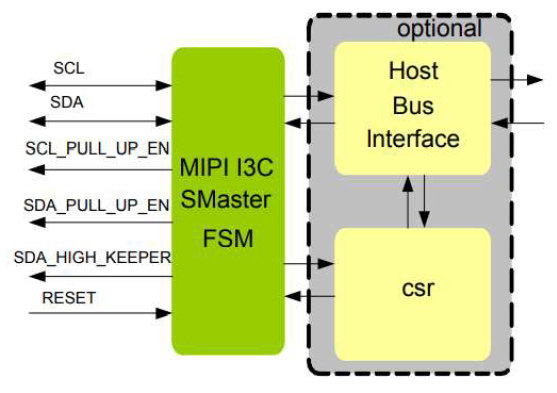

The I3C SMaster IP Core is full-featured, easy-to-use, synthesizable design that is easily integrated into any SoC or FPGA development. The I3C SMaster IP can be implemented in any technology. The SMaster IP core supports the I3C version 1.1 and I3C HCI version 1.1 specifications. It can also support a variety of host bus interfaces for easy adoption into any design architecture - AHB, AHB-Lite, APB, AXI, AXI-Lite, Tilelink, OCP, VCI, Avalon, PLB, Wishbone or custom buses. The SMaster IP is delivered in Verilog RTL that can be implemented in an ASIC or FPGA. The SMaster IP is validated in using FPGA. The core includes RTL code, test scripts and a test environment for complete simulation.

Features

-

Compliant with MIPI I3C version 1.1 and I3C HCI version 1.1 specifications.

-

Compliant with JEDEC Module Sideband Bus version 1.0 specification with PEC code and CCC transfers.

-

Compliant with MCTP I3C Transport Binding version 3.0 specification with counters for IBI in Slave Mode.

-

Non HCI Version is also supported for designs which are gate count sensitive.

-

Full MIPI I3C Master, Secondary Master and Slave Functionality.

-

Two wire serial interfaces up to 12.5 MHz

-

Supports all topologies • Single Master – Multi Slave • Single Master – Single Slave • Multi Master – Single Slave • Multi Master – Multi Slave

-

Dynamic Addressing while supporting Static Addressing for legacy I2C device.

-

Supports Master Pull up structures.

-

Supports I3C address arbitration optimization.

-

Supports Predictive addressing scheme

-

Supports Direct commands

-

Supports Direct command CCC framing

-

Supports Single Data Rate (SDR) messaging. • SDR with Direct CCC • SDR with Broadcast CCC

-

Supports High Data Rate (HDR) messaging • HDR-Dual Data Rate Mode (HDR-DDR) • HDR with Direct CCC • HDR with Broadcast CCC • HDR-Ternary Symbol for Pure Bus Mode • HDR-Ternary Symbol Legacy-inclusive Mode

-

In-Band Interrupt support, Hot-Join and Secondary Master interrupt support

-

Auto-Reject for In-Band Interrupt and Hot-Join

-

Legacy I2C Device co-existence on the same Bus instance

-

Direct Data interface support (PIO Mode) • Command Queue for Command Descriptors • Response Queue for Response Descriptors • IBI Queue for both IBI status and IBI data

-

DMA interface support (DMA Mode) • Single transfer descriptor defines Command and Data • Single response status descriptor reports status of the transfer • Linked descriptor support (Multicast messaging support

Deliverables

-

The I3C SMaster IP interface is available in Source and netlist products.

-

The Source product is delivered in plain text Verilog. If needed VHDL, SystemC code can also be provided.

-

Easy to use Verilog Test Environment with Verilog Testcases

-

Lint, CDC, Synthesis, Simulation Scripts with waiver files

-

IP-XACT RDL generated address map

-

Firmware code and Linux driver package

-

Documentation contains User's Guide and Release notes.