## eFPGAs Bring a 10X Advantage in Power and Cost

eFPGA LUTs will out ship FPGA LUTs by the end of the century because of the advantages of reconfigurable logic being built into the chip: cost reduction, lower power and improved performance.

Many systems use FPGAs because they are more efficient than processors for parallel processing and can be programmed with application specific co-processors or accelerators typically found in datacenters, wireless base stations and enterprise storage.

The need for improved processing in the cloud is driven by faster search results which drives revenue. FPGAs provide very valuable programmability in these systems but customers would like to find a way to reduce the power and size to increase compute density. The way to achieve this is to integrate the FPGA into the companion SoC.

Why? Because it saves power and cost by as much as 10X. The 10X in cost reduction does not even include the saving from inventory reduction and testing when there is an extra chip on the board. For example, integrating the FPGA can reduce costs from \$300 down to 20\$ of additional silicon cost and the power similarly.

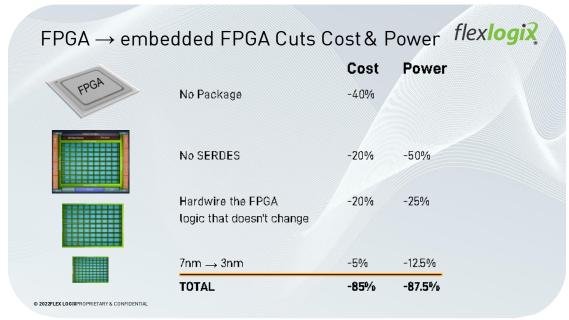

Fig. 1 eFPGA cuts power and cost by as much as 10X

In Fig.1, we break down the example steps to assess how the cost and power reduction for an SoC + FPGA processing solution. As most chip designers know, the packaging is a significant cost for each chip. Integrating the FPGA removes the packaging cost savings could be as much as 40% of the cost of the FPGA chip which ranges from tens to hundreds

## eFPGAs Bring a 10X Advantage in Power and Cost

of dollars. In an integrated solution, only one chip needs to be packaged which is already factored into the cost of the main processing SoC. Normally in the pricing of chips, everything is marked up, including packaging. FPGAs are no different so conservatively we did not include that.

Next, we can remove the SerDes in the FPGA as these are not needed anymore because there is no separate FPGA chip. All the communication between the eFPGA and processor subsystem will happen directly within the SoC. Analog I/O PHYs used in the FPGA chip are no longer present which can be a large reduction in cost and even a larger savings in power. Also, without the signals having to travel through a SerDes on both sides, latency is reduced. This can be critical for some applications such as searches and data look-ups where latency through one high-speed SerDes can be as much as 20-30 clock cycles. Since the SerDes inside the SOC is also not needed that latency reduction is double that!

In every FPGA design, there is logic that does not change but since you have a single FPGA for much of the design it's easier to include the entire design as one big blob into a sea of LUTs. SOC integration and eFPGA provides an opportunity to rethink how the FPGA design is partitioned so you can leverage the area, power and performance benefits of ASIC gates by putting those fixed logic components into the SOC as hardwired logic. This can be conservatively estimated at 20% of the silicon area but some designs will be more savings of cost and power.

Technology is getting smaller and smaller and this is providing the opportunity of reducing the total cost of ownership by going to smaller nodes. Embedded FPGA made with 100% standard cells can be ported quickly to reduce area, cost and power of the final SOC as noted in the figure. This is at a pace that is much faster than FPGA providers who utilize full custom design which can take several years to move to a new technology node.

Flex Logix has the best eFPGAs because we provide a hard macro that sits in the lower layers of the metal stack and is compatible with most metal stacks offered in a foundry's process. Flex Logix eFPGAs save power and area using our patented Boundless Radix interconnect. This interconnect results in shorter paths, less area and higher utilization of the eFPGA. Also, we can offer different types of power gating to lower power even further. By proving a completely hardened design, we simplify the closing of timing for the customer and ease their integration of the eFPGA.

So, the next time you are looking to reduce cost and power in your System think about including eFPGA and for the most power reduction and ease of integration think EFLX® eFPGAs from Flex Logix.