Debug and Test Solutions

Home > Interface IP > PCI Express Controller IP > Debug and Test Solutions

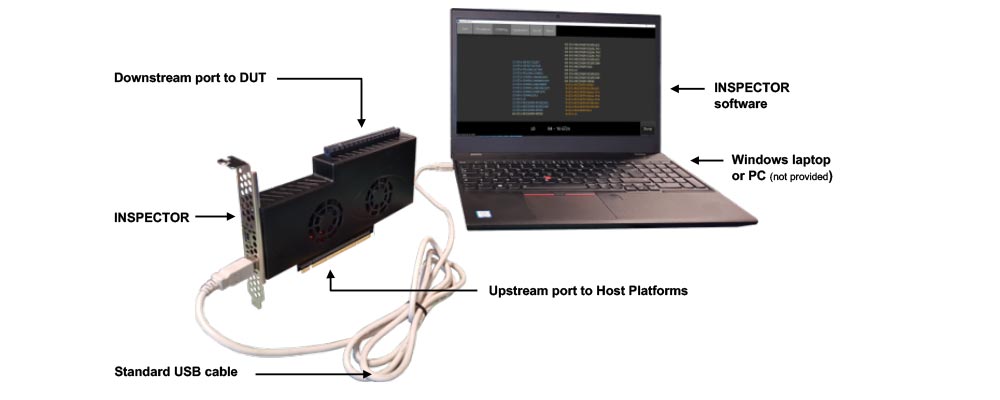

INSPECTOR for PCIe 5.0

Interposer Card for Diagnostic Testing, Exercising and Debug of PCIe Devices at up to Gen5 32 GT/s speed.

INSPECTOR is a PCIe 5.0-compliant interposer module designed for non-intrusive monitoring, diagnostic, exercising and debug of PCIe devices. INSPECTOR uses transparent switching technology to connect on the upstream side to a PCIe host platform, and on the downstream side to the device under test (DUT). INSPECTOR supports PCIe 1.x, 2.x, 3.x, 4.x and 5.0 interfaces on either ports, and up to 4 lanes (x4) at maximum data rate. It is typically used for bring-up and diagnostic testing of PCIe 5.0 DUTs at PCIe 5.0 32 GT/s speed using existing PCIe hosts operating at PCIe 4.0 16 GT/s speed, but can support any link speed/width combination on upstream and downstream ports. INSPECTOR’s built-in diagnostic capabilities allow validation engineers to instantly diagnose issues with their PCIe devices, without the need for expensive test equipment.

Watch this video and learn how to test and debug PCIe 5.0 devices with Inspector

Gen5HOST

PCIe 5.0 Host Enabling Reference Platform for Prototyping & Development of PCIe 5.0 Devices and Applications.

Gen5HOST provides a platform for prototyping and developing PCIe 5.0 hardware and software. At the core of Gen5HOST is the Rambus PCIe 5.0 Switch IP running on a Xilinx® Virtex® UltraScale+™ FPGA. Gen5HOST provides a PCIe 4.0 x8 (upstream) to PCIe 5.0 x4 (downstream) integration backplane for development and validation of PCIe 5.0 endpoints, and is also available in a reversed configuration (PCIe 5.0 upstream, PCIe 4.0 downstream) for development and validation of PCIe 5.0 Hosts and Root Complexes. By working with Gen5HOST, developers of PCIe 5.0 devices can accelerate their software, firmware, and hardware developments, in their production environment, using the operating system of their choosing.

Gen5ENDPOINT

PCIe 5.0 Endpoint Reference Platform for Prototyping and Development of PCIe 5.0 Root Port/Host Silicon and Devices.

Gen5ENDPOINT is a PCIe add-in card suitable for prototyping and developing PCIe 5.0 hardware and software. At the core of Gen5ENDPOINT is the Rambus PCIe 5.0 Switch IP running on a Xilinx® Virtex® UltraScale+™ FPGA. Gen5ENDPOINT features an integrated PCIe 5.0 endpoint agent with DMA and memory-mapped I/O capability. By working with Gen5ENDPOINT, developers of PCIe 5.0 host systems and root complexes can accelerate their software, firmware, and hardware developments, in their production environment, using the operating system of their choosing.

Data Center Evolution: The Leap to 64 GT/s Signaling with PCI Express 6.1

The PCI Express® (PCIe®) interface is the critical backbone that moves data at high bandwidth and low latency between various compute nodes such as CPUs, GPUs, FPGAs, and workload-specific accelerators. With the rapid rise in bandwidth demands of advanced workloads such as AI/ML training, PCIe 6.1 jumps signaling to 64 GT/s with some of the biggest changes yet in the standard.

Resources

Testing and debugging PCIe 5.0 devices with Inspector