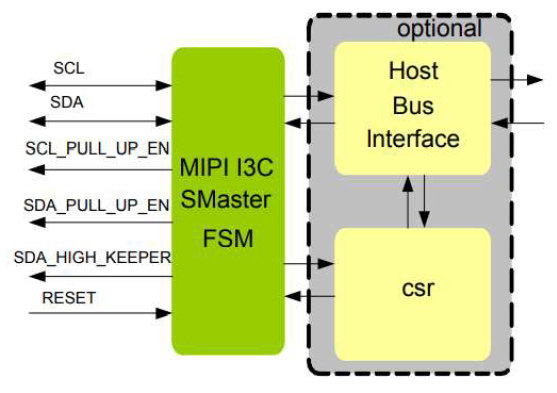

I3C SMaster IPå ·æåŪåĪįåč―ïžč―åĪįŪåįéæå°äŧŧä―SoCæFPGAįåžåäļãI3C SMaster IPåŊäŧĨåĻäŧŧæäļį§ææŊäļåŪį°ãI3C SMaster IPįŽĶåI3Cv1.1åI3C HCIv1.1č§čãæĪåĪïžčŋäļŠIPåŊäŧĨæŊæåĪį§äļŧæšæŧįšŋæĨåĢïžč―åĪæđäūŋå°éæå°ææčŪūčŪĄä―įģŧįŧæäļ——AHB, AHB-Lite, APB, AXI, AXI-Lite, Tilelink, OCP, VCI, Avalon, PLB, Wishbone æčŠåŪäđåčŪŪįãSMaster IPåĻVerilog RTLäļäšĪäŧïžåŊäŧĨåĻASICæFPGAäļåŪį°ãSMaster IPéčŋFPGAįéŠčŊïžäšĪäŧäŧķå æŽRTLäŧĢį ãæĩčŊčæŽåįĻäšåŪæīäŧŋįįæĩčŊįŊåĒ.

įŽĶåMIPI I3C v1.1åI3C HCI v1.1įč§čã

įŽĶåJEDECæĻĄåčūđåļĶæŧįšŋ1.0įč§čïžå ·æPECäŧĢį åCCCäž čūã

įŽĶåMCTP I3C Transport Binding 3.0įč§čïžåĻäŧåąæĻĄåžäļå ·æIBIįčŪĄæ°åĻã

éHCIįæŽäđæŊæåŊđéĻæ°ææįčŪūčŪĄã

åŪæīįMIPI I3CäļŧįŦãæŽĄįŦåäŧįŦåč―ã

äļĪįšŋäļēčĄæĨåĢïžéĒįéŦčūū 12.5 MHzã

æŊæææįææįŧæ--åäļŧ-åĪäŧ-åäļŧ-åäŧ-åĪäļŧ-åäŧ-åĪäŧ-åäŧ-åĪäļŧ-åĪäļŧ-åĪäŧ

åĻæåŊŧåïžåæķæŊæäž įŧI2CčŪūåĪįéæåŊŧåã

æŊæäļŧæåįŧæã

æŊæI3Cå°åäŧēčĢäžåã

æŊæéĒæĩæ§åŊŧåæđæĄ

æŊæįīæĨå―äŧĪ

æŊæįīæĨå―äŧĪCCCææķ

æŊæåæ°æŪéįïžSDRïžäŋĄæŊäž éã- åļĶæįīæĨCCCįSDR - åļĶæåđŋæCCCįSDR

æŊæéŦæ°æŪéįïžHDRïžäŋĄæŊäž é - HDR-åæ°æŪéįæĻĄåžïžHDR-DDRïž - åļĶæįīæĨCCCįHDR - åļĶæåđŋæCCCįHDR - įšŊæŧįšŋæĻĄåžįHDR-äļå įŽĶå· - HDR-äļå įŽĶå·éįįæĻĄåž

åļĶå äļææŊæïžįčŋæĨåäšįš§äļŧæ§äļææŊæ

åļĶå äļæåįčŋæĨįčŠåĻæįŧåč―

Legacy I2CčŪūåĪåĻåäļæŧįšŋåŪäūäļå ąåã

Directæ°æŪæĨåĢæŊæïžPIOæĻĄåžïž - įĻäšå―äŧĪæčŋ°įŽĶįå―äŧĪéå - įĻäšååšæčŋ°įŽĶįååšéå - įĻäšIBIįķæåIBIæ°æŪįIBIéå

DMAæĨåĢæŊæïžDMAæĻĄåžïž - åäļäž čūæčŋ°įŽĶåŪäđå―äŧĪåæ°æŪ - åäļååšįķææčŋ°įŽĶæĨåäž čūįįķæ - éūæĨæčŋ°įŽĶæŊæïžæŊæįŧææķæŊ

äšĪäŧäŧķ

I3C SMasterįIPåŊäŧĨäŧĨæšäŧĢį åį―čĄĻįå―ĒåžæäūįŧåŪĒæ·

æšäŧĢį åŊäŧĨäŧĨVerilogčŊčĻæ žåžįææŽæäūįŧåŪĒæ·ïžåĶæåŪĒæ·éčĶVHDLïžSystemCčŊčĻæ žåžįææŽäđåŊäŧĨæäū

åŪđæä―ŋįĻįVerilogæĩčŊįŊåĒåVerilogčŊčĻįžåįæĩčŊįĻäū

LintãCDCãįŧžåãäŧŋįčæŽäŧĨåé åĨįWaiveræäŧķ

æ đæŪIP-XACT RDL 䚧įįåŊååĻå°ååčĄĻ

åšäŧķäŧĢį åLinuxéĐąåĻįĻåšå

äšĪäŧææĄĢå æŽįĻæ·æååįæŽæå