概述和功能介绍

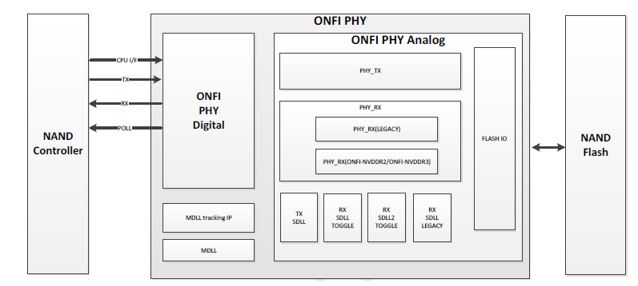

ONFI PHY IP能够通过NAND闪存接口传输信号,或通过Flash控制器IP从NAND Flash接收数据。MDLL为PHY的控制信号设定延迟时间,以便在合适的时间段内访问闪存中的数据。请参考下图,了解ONFI PHY的架构

.

功能描述

-

支持ONFi 4.1 IO规范

-

支持高达50MHz的遗留

-

支持NV-DDR2,533Mbps的数据传输

-

支持NV-DDR3,1200Mbps的数据传输

-

用于控制偏移的每DQ(每比特)延迟线

-

包括SDLL,通过DLY设置进行DQS/DQ相位调整

-

通过芯片上的去耦电容(每通道>1nF)以节省PKG电容,具有电源完整性

-

工作温度:-40至125°C

-

翻转芯片

-

支持的金属方案:

-

1P9M_2Xa1Xd3Xe2Z

-

1P10M_2Xa1Xd4Xe2Z

![]()