Description and Features

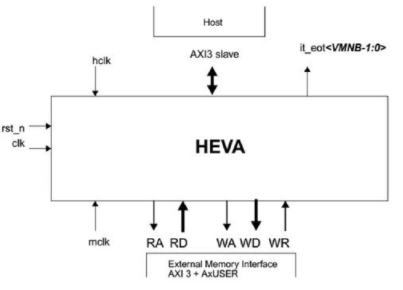

The Hardware Encoder Video Accelerator (HEVA), supports HEVC encoding low complexity with a flexible architecture targeting at least 1080p60 with minimal processing units and memory cuts and up to 2160p120 with large number of units and large memory cuts. Trade-off performance/area at design configuration: Reference cache size for 2160p30 at 350 MHz, 1 reference frame and bandwidth, overhead of 100% for references i.e. 1.5 GBytes/sec (minimal is 1.2 GB/s) Hardware interfaces :Host interface AXI3/AXI4 slave interface for the registers and command/status FIFO, Memory interface AXI3/AXI4 Streaming interfaces to External DRAM, Asynchronous AXI3/AXI4 128 bits interface, Synchronous DMA arbiter and memory interface Task sequencing modules: Manages communication and storage between processing modules, Control the shared memories and caches between the TPU modules and TSU/MIF, Defines the execution mode of the task processing units Task processing modules: Perform the pixel and bit-stream processing under control of TCR/TSU, The number of processing elements is defined at design configuration to sustain the required performance, A local reference cache is needed for performance for some processing units.

Features

-

Encoder acceleration

-

Performance up to 330 Mpixel/sec (2160p30 + 1080p30)

-

HEVC Main support, Level 4.2 (2160p30)

-

H.264 High Profile Progressive, Level 5.1 (2160p30, 1080p120)

-

HEVC Sample Adaptive Offset in-loop deblocking

-

Full coding unit support (from CU 64x64 to CU 8x8, PU 4x4)

-

No restriction on MV range allowed (X<8192, Y<4096)

-

Slice support: single slice or number of CTB lines per slice

-

Slice level IT programmable

-

Original input frame

-

Bottom/Right original padding on-the-fly

-

YUV 420 semi-planar: NV21

-

Reference frame usage

-

Internal 2D frame format

-

Optional proprietary lossless compression on reconstructed/reference frames

-

Up to two reference frames

-

Generalized P/B frames for low delay encoding

-

GOP up to 8 frames hierarchical B-frames for random access encoding

-

Motion vector range not limited, trade-off bandwidth versus MV range up to the application programming and design configuration.

-

Programmable quality/performance trade-off

-

Optional user defined input parameters

-

Deblocking slice parameters

-

User defined quantization scaling matrix tables

-

Chroma QP offsets

-

Region of interest input map table

-

Motion vector of Interest input map table

-

Optional user report output

-

Motion vector field

-

with/without Basic picture analysis

-

Latency tolerance at design configuration

Deliverables

-

RTL Source Code

-

HDL based test bench and behavioral models

-

Test cases

-

Protocol checkers, bus watchers and performance monitors

-

Configurable synthesis shell

-

Documentation & Design Guide

-

Verification Guide

-

Synthesis Guide

Applications

-

HEVC & H264 Recorder & Transcoder, for NAS application for Set Top Box application Best in Class HEVC Transcoder .

-

HEVC & H264 Video monitoring on video surveillance sequences –

-

On outdoor, non-static sequences ~5 to ~10% of bit-rate reduction

-

On outdoor, static sequences ~10 to 20% of bit-rate reduction

-

On indoor & lowlight sequences ~10% of bit-rate reduction

![]()