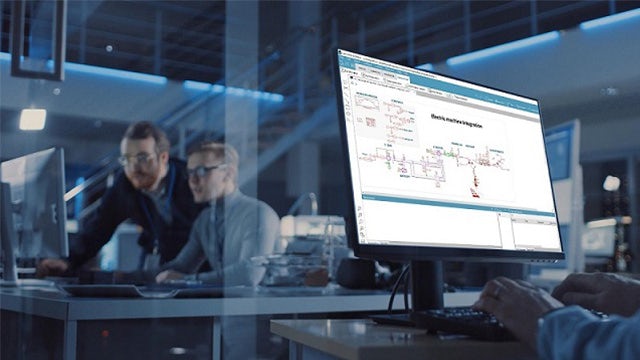

Access critical insights and forensic capabilities to manage the risk of building embedded systems with processor trace. The Tessent Enhanced Trace Encoder is a market-leading solution for RISC-V, designed to meet the official RISC-V trace specification.

This solution builds on the RISC-V standard produced by the Debug and Trace Working Group, which was led by representatives from Siemens who donated the trace algorithm to the RISC-V International community.

The Tessent Enhanced Trace Encoder goes well beyond the RISC-V standard. Get significant productivity gains in the development of complex systems, and access insights into each and every instruction since it is cycle accurate.