Warren: Stephen, good to talk with you again. Can you share a little background on yourself and how you got into the IP business?

Stephen: Well, I have been doing ESD and IO designs for the last fifteen years. In 2006, I started SRF Technologies as an ESD consulting firm specializing in high frequency RF and analog products. We’ve since expanded SRF Technologies to a design center delivering custom IO pad libraries for all areas of the industry, not just analog and RF.

As far as providing IP, we kind of fell into it. As it happened, different clients began requesting similar designs, and though it was never our intent, we found it useful to package designs as proven IP blocks.

However, because ESD’s and IO’s are so specific, the vast majority of our work is still customizing our IP blocks for specific applications. Every SoC has characteristics that allow us to take our proven IP and tweak it for footprint, area, or power, depending on the application. In that way, we have stayed true to our roots as a custom IO and ESD design service.

WS: So, how would you rate the experience of working in IP versus other jobs you’ve held?

SF: That is a hard question for me to answer, because there are aspects of the IP business that are much easier to deal with than full custom. On the other hand, there are also aspects of the IP business that are a lot harder and sometimes more frustrating than full custom. It almost depends on the customer’s application and—let’s be honest—their tools. It feels like we spend fifty percent of our time debugging tool issues.

WS: There has been tremendous consolidation of the IP market in recent years, with a number of the small and medium players getting gobbled up by the big guys. What does this tell us?

SF: The big guys buy the smaller guys for the simple fact that the smaller guys provide value. They’re doing something the bigger guys don’t do as well, and it’s actually cheaper for the bigger guys to buy the smaller guys than to try and build up the expertise in-house. The real question I ask myself is: once they’re swallowed up, how well do they deliver to their customers? I still think there is a viable market for smaller IP companies because they tend to provide better support and customer response. The larger IP companies generally are only looking to support large customers; they have a lot of overhead. The smaller companies and startups purchasing IP tend to get tossed by the wayside when they need real service.

WS: The tech media of today, at least in the US, seems to have drastically shrunk. Famous editors are now working for product companies. How do you get your message out to customers in such an environment?

SF: I have never had a good answer to that. We are still trying to figure out how we should go out and market ourselves most effectively to potential customers. The reality is, our business over the last six years has been built completely by word of mouth and personal references.

WS: What’s the biggest change you’ve seen in the market since the meltdown of late 2008?

SF: Design cycle times have been dramatically cut. It’s made the issue of getting it right the first time a bigger priority. The challenge here is that people expect IP to be easily pulled off the shelf and dropped in and work. Conceptually, that would be ideal. The reality is that integrating IP is still a big challenge, and finding IP that meets your exact specifications is difficult. You have these compounding issues of finding the exact IP that meets your needs, making sure it integrates with your tools and design database correctly, and making sure that it covers all your usage models. And then you have to get it right. The first time. And in less time. I should add a caveat here: these challenges are probably harder when it comes to the analog and IO space because you see a wide range of voltages and usage models, even on the same process.

WS: It wasn’t long ago that many IP companies were worried about licensing IP to China. Has that changed post-2008?

SF: It’s mixed. From personal experience, I know some companies that are still concerned about it and others that aren’t concerned at all. I think it depends on the type of IP they’re offering, but I would say that most people still expect that some kind of IP theft will occur when licensing to China.

WS: Let’s bring out our crystal ball for a moment. What you predict will be the biggest, most disruptive change in semiconductors in the next three years?

SF: I actually don’t see any major disruptive changes on the horizon. I think all the hot new technologies people have discussed are still too far off from affecting the mass production and cost maturity of current semiconductor technology. Barring a revolutionary technology breakthrough, I think we will see more of the same evolutionary development of the semiconductor industry as we have over the past fifteen years.

I do foresee that reliability and DFM for cutting-edge technology nodes will be much harder than expected for most companies. This is in spite of the fact that everyone knows and talks about how much harder it is to design below 40nm. Particular to our area of expertise, despite many in the industry reducing ESD standards, we are seeing an increase in EOS and field failures for products at these nodes.

WS: It seems like there just a ren’t any hot new startups anymore, while even industry titans are merging, as we saw with Texas Instruments’ recent acquisition of National Semiconductor. Are you apprehensive about such consolidations in the semiconductor industry?

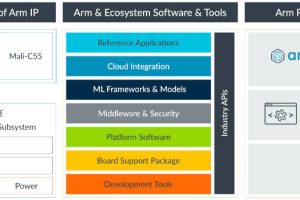

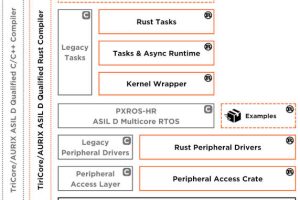

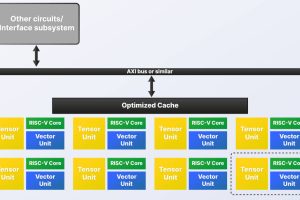

SF: I am not apprehensive about the consolidations; I think they reflect the nature of the industry. The problem you have nowadays is that in order to introduce a semiconductor product, you have to have an ecosystem built around it. Take, for example, apps processors or DSP’s. All of them require a huge supporting environment of software, PDK’s, and development tools. This type of environment is something a small startup company can’t compete with. It is hard enough developing your IC, much less supporting tools and ecosystems, on a startup budget.

To top it off, you have the challenge of getting customers, already used to the PDK’s, development tools, software, and ecosystems of current products, to decide to throw all that expertise and background away and try a new system. It’s a major risk to product development cycles.

If you were to create a really novel microprocessor architecture, you would likely only find a market in niche spaces where it wasn’t already dominated by all of the supporting ecosystem that you can find with ARM or X86. So what you see now is that startups are almost universally looking at niche technologies or technologies that don’t require a unique ecosystem, such as PMIC’s, specialty analog devices, RF components, sensors, or MEM’s. These products are easily adopted into existing ecosystems. It is very difficult in today’s environment for a small start-up to create a new ecosystem to support their hot new product, so you see a lot of startups looking to supplement the current ecosystems. If they do well and their designs get adopted, they get bought up by the owners of those larger ecosystems.

WS: What would be your recommendations for new EE grads coming into the semiconductor world today?

SF: Learn Verification. It seems we cannot find enough good verification engineers, and the demand will only grow as our products become increasingly complex. In fact, one of the biggest challenges of an IP provider is helping customers run verification with your block.

WS: Before we go: three words that you would use to describe the semiconductor industry today.

SF: Expensive, rushed, and exciting.

WS: Stephen, thanks so much for sharing your thoughts with us today.

About Stephen Fairbanks, President, SRF Technologies; and Co-Director, Certus Semiconductor

With nearly fifteen years of experience designing systems and products to interface to each other while withstanding the rigors of ESD and EMI susceptibility, Stephen brings a unique and honed skill set that his customers can leverage.

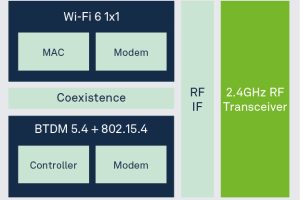

In the semiconductor industry, he has been developing process specific I/O and ESD libraries for twelve years. Most notable were his efforts at Intel Corporation, where he was the lead developer of the ESD and I/O libraries for what were then Intel’s wireless, cellular, and mobile computing groups. He led the development of IO and ESD used on the initial and many subsequent generations of the wireless components (MAC basebands and RF Front Ends) for the Intel Centrino chipsets. Stephen was also personally responsible for the ESD development and I/O support for three families of cellular communications processors and four families of handheld applications processors. He has developed ESD process design rules, ESD libraries, and IO libraries in Logic, RF and Mixed-signal processes at the 0.25um, 0.18um, 0.13um, 90nm, 65nm, 45/40nm and 28nm processes. Stephen is also familiar with several specialty processes, including HV BiCMOS, Flash memory, SiGe, SOI, SOS and InP.

Apart from ESD and IO design, Stephen has done significant work in system design, including compliance testing to standards such as CE, UL and other international standards.

See also:

Warren Savage On: Catching up with Jack Browne

Electronics Weekly Electronics Design & Components Tech News

Electronics Weekly Electronics Design & Components Tech News