PCI Express: Delivering Needed Bandwidth for Open Compute Project

By Al Yanes, PCI-SIG President and Chairman

I recently attended the OCP Summit for the first time and I was impressed by the size of this growing event. The San Jose Convention Center was packed with industry experts – all eager to discuss how to move the Open Compute Project (OPC) forward. I had the opportunity to present on how PCI Express® technology is meeting OCP needs for more and more bandwidth, as well as meet with attending press and analysts to discuss trends in I/O technology, form factors and what’s next for the industry as bandwidth demands continue to explode.

The PCIe 4.0 specification – finalized and published in 2017 – is designed to meet these growing bandwidth demands. PCIe 4.0 architecture delivers 16GT/s with scalable performance up to x16 width, delivering 64GB/s. We’ve seen healthy adoption to date from our members and PCI-SIG is currently working on its PCIe 4.0 Compliance Suite and will publish its Integrator’s List later this year.

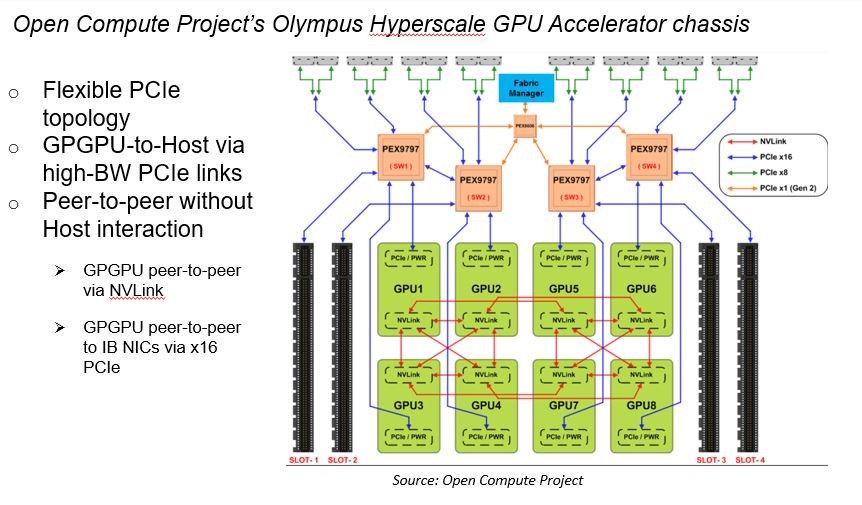

So what does this mean for OCP? The PCIe architecture is used across the OCP ecosystem. At least year’s event, the OCP Olympus Project –just one example of many where PCIe technology is implemented – showcased a GPU Accelerator chassis that included PCIe 3.0 x16 links – as seen in the diagram below.

PCI-SIG has been diligent about ensuring that our specifications are backward compatible. Therefore all of the PCIe 3.0 links in the Olympus chassis can be readily replaced with PCIe 4.0 links to double the bandwidth. For OCP, this means that designers can invest in PCI Express technology, and still be enabled for the generations to come – not just PCIe 4.0, but PCIe 5.0 technology as well.

The PCIe 5.0 specification, announced in June 2017, is on the fast track with a targeted specification completion date the first half of 2019. And we’ll be releasing the PCIe 5.0 0.7 specification to members in the near future. Targeted at speed enhancements, PCIe 5.0 will deliver 32GT/s, or up to 128GB/s at x16. Both PCIe 4.0 and 5.0 specifications in x16 mode meet the needs of 400Gb Ethernet solutions by delivering 50GB in both directions.

|

RAW BIT RATE |

LINK BW |

BW/LANE/WAY |

TOTAL BW X16 |

|

|

PCIe 1.x |

2.5GT/s |

2Gb/s |

250MB/s |

8GB/s |

|

PCIe 2.x |

5.0GT/s |

4Gb/s |

500MB/s |

16GB/s |

|

PCIe 3.x |

8.0GT/s |

8Gb/s |

~1GB/s |

~32GB/s |

|

PCIe 4.0 |

16GT/s |

16Gb/s |

~2GB/s |

~64GB/s |

|

PCIe 5.0 |

32GT/s |

32Gb/s |

~4GB/s |

~128GB/s |

PCI-SIG, with 750+ member companies strong developing open industry standards, will continue to deliver the needed bandwidth that OCP and our members need. If you’d like to help participate in the specification development process, I encourage you to join us. To learn more about how we’re enabling OCP architectures and the PCIe specifications, you can watch my presentation here, or download the slides here.