Design IP, at least Interface IP, is about 15 years old, but the market was made of one large provider – Synopsys- with many small vendors around. Chip makers were not very comfortable with this picture, especially the Tier 1 considering that the risk (to see the big one being acquired by one of their direct competitor, say Samsung or Intel) was unacceptable. This was the picture in 2010: Synopsys leader on every Interface IP segment, Cadence leader in Verification IP, but only in VIP, and many small IP vendors acting like an electron cloud around Synopsys atom… Moreover, the market value of design IP was 5X the VIP market value, and this is still the case!

You have to keep in mind that building a design IP port-folio is far to be easy: ask Mentor Graphics why they had to give up in 2007, after 10 years of engineering effort. In 2010, Cadence has passed a clear message to the market, with Denali acquisition (for $300M +), but this message has been blurred when the company spoke about “EDA 360”. Design IP is a particular piece of the equation as it goes in a Chip which, in turn, goes to a wafer-fab, when Software, as important as it can be to release a product, is not as critic as a Design IP is.

The venue of Martin Lund (from Broadcom, known to deliver chips, not only paper, to the market) in Q2 2012 to take care of the “Silicon Realization Group” within Cadence has shuffled strong energy to cadence IP strategy. Martin has probably visited many IP vendors companies during 2012, then 2013 has been the time for finalization. Tensilica, provider of customizable DSP or CPU IP cores, has been the first in the list, being acquired by cadence in March 2013. Very interesting to notice, Simon Segars was quoted in the PR mentioning this acquisition… If you want to build a successful IP strategy, it’s probably better not to directly attack the undisputed leader, ARM Ltd.

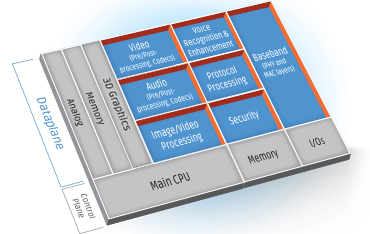

Almost at the same time came the announcement that cadence was acquiring Cosmic Circuit, India based mixed-signal IP vendor, providing DAC and ADC, and Interface IP PHY supporting MIPI M-PHY and D-PHY and SuperSpeed USB PHY. If you look at the above picture, Cosmic brings the blue-boxes, that you will find in almost every SoC today. But that was not enough! Denali acquisition allowed supporting many more protocols Verification, but only two Design IP: DDRn Memory Controller and PCI Express.

Then came the first announcement during CDN-Live, on Tuesday this week, Evatronix acquisition. Box colors have changed in the meantime, but the principle stay the same: Evatronix acquisition brings the green colored boxes, USB 2.0 and USB 3.0 controllers, some MIPI controllers , eMMC and SDCard. You may have the impression that Martin Lund, above pictured, looks tired: the acquisition contract with Evatronix was signed during Sunday night, right on time for CDN-Live! According with Wosjiech Sakowski, Evatronix co-founder and President, the signature came after long hours –days – of negotiations.

But I keep very interesting acquisition related news, which was made public during CDN-Live as well, even if it was effective a few weeks ago: Cadence has bought, not a company, but an Engineering team. This 25 Engineers Canadian based team from PMC-Sierra is 100% specialized in SerDes design, and you can guess that they don’t limit to 5 Gbps PHY. Why is this news so strategic? Because PHY is strategic, as I already claimed in Semiwiki here.

Just remember that Synopsys had to buy a PCIe 8 Gbps PHY to MoSys last year to be able to support customers. This design team is probably capable to manage 25 Gbps SerDes (my guess). In this case, half a dozen IP sales from this team could generate Evatronix per year revenue, made of multiple dozens of controller IP sales. But that’s not the most important: this who manage properly the PHY IP business will manage to get higher market share of Integrated (PHY + Controller) Interface IP sales, now and for the future; especially in the future.

Eric Esteve from IPNEST

lang: en_US

Share this post via:

Comments

0 Replies to “Design IP round #2: after road-test, time for the race”

You must register or log in to view/post comments.