The semiconductor industry is experiencing unprecedented growth, driven by the increasing complexity of today’s chip designs. Advanced systems-on-chip (SoCs) now integrate over 300 intellectual property (IP) blocks, pushing design challenges to new levels. The rapid adoption of AI-driven automotive safety systems and the expansion of edge AI and IoT applications further highlight the demand for energy-efficient network-on-chip (NoC) solutions. This rising complexity requires a new level of scalability, especially for cutting-edge process nodes at 5nm, 3nm and beyond, where optimizing power, performance, and area (PPA) is essential.

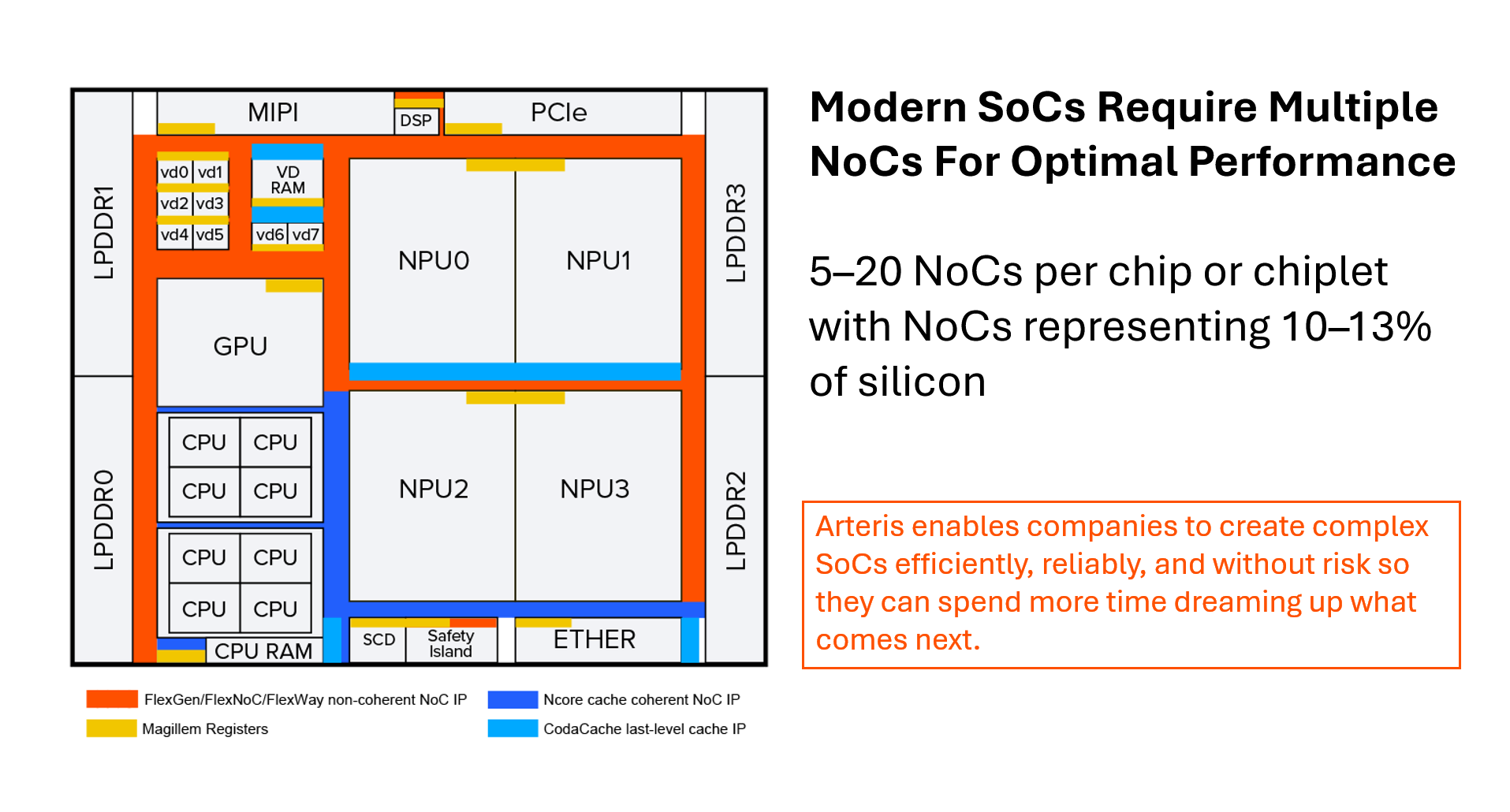

Typically, SoCs now comprise between 5 to 20 individual NoC instances, occupying approximately 10-13% of the total silicon area. Current methodologies, combined with increasing register requirements, are becoming insufficient. As a result, designers face lengthy development cycles, repeated iterations, and significant schedule risks. Given these limitations, automated NoC generation offers a scalable solution to manage escalating design challenges.

Image 1. Today’s SoCs require multiple NoCs for optimal performance. (Source: Arteris)

Automated NoC Generation

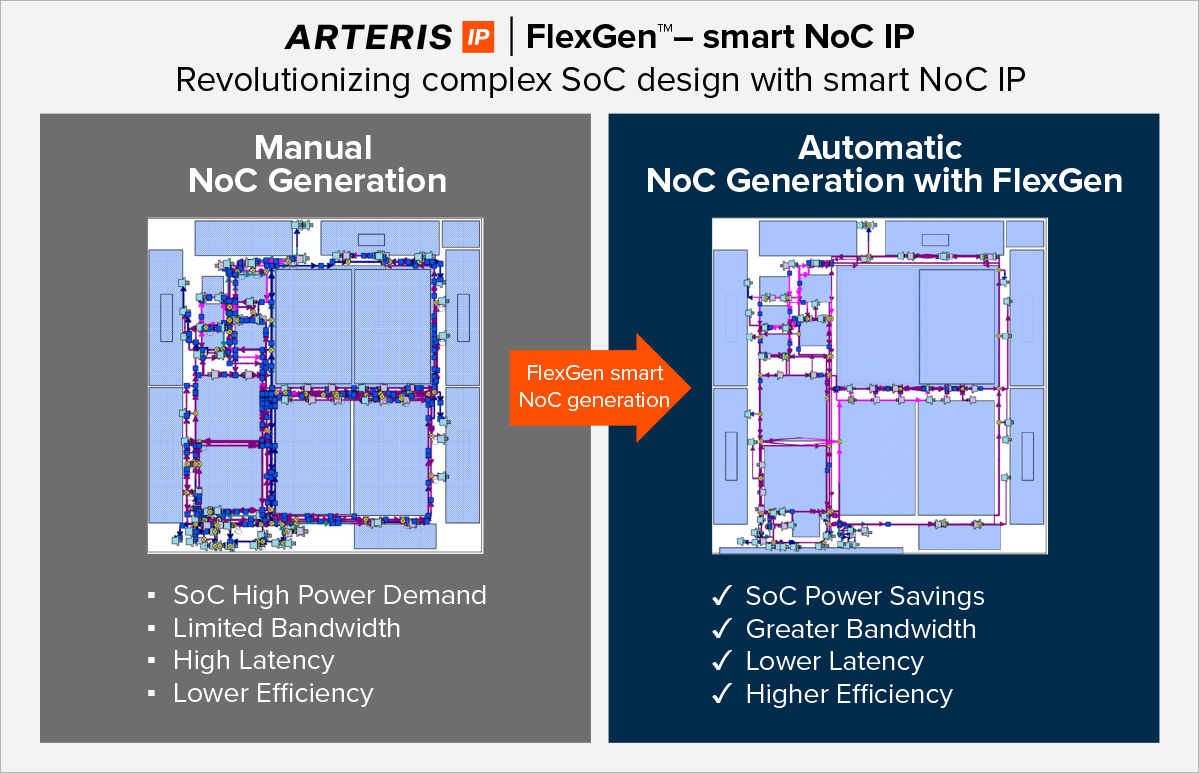

To address these industry-wide issues, Arteris has developed FlexGen™ smart NoC IP, which uses advanced algorithms and AI-driven automation of NoC interconnect design and optimization. This technology reduces reliance on traditional manual design processes, enabling efficient management of modern SoC requirements.

By automating NoC design, teams can streamline development, achieving significant productivity gains while reducing manual effort. Typically, manual NoC designs require multiple adjustment cycles, often spanning weeks. With automation, design iterations can be completed in hours. This allows design teams to initiate physical layout earlier and evaluate architectural alternatives more rapidly. Shorter cycles directly translate into faster development timelines, accelerating time to market and mitigating schedule risks.

Performance and Efficiency Improvements

In addition to improving productivity, FlexGen enhances PPA metrics. This technology leverages advanced algorithms to optimize interconnect design, reducing wire lengths by up to 30% compared to traditional manual methods. This reduction improves power efficiency, signal integrity, and latency, contributing to overall SoC performance.

Reducing congestion enhances bandwidth, ensuring high throughput and reliable performance across densely integrated IP blocks. In a recent automotive advanced driver-assistance systems (ADAS) SoC application, an automated NoC design with FlexGen demonstrated a 26% reduction in total wire length with a 28% decrease in the longest wire, resulting in lower latency and improved silicon area efficiency. While these PPA improvements are significant, seamless integration is equally essential for adapting NoC architectures to diverse SoC requirements. This flexibility supports processor architectures and interconnect topologies, enabling efficient adaptability to application requirements.

Image 2. FlexGen smart NoC IP revolutionizes complex SoC designs. Source: Arteris)

Integration Flexibility

FlexGen smart NoC IP builds on Arteris’ proven FlexNoC IP, delivering broad compatibility and seamless integration, supporting industry-standard protocols like AMBA 5 ACE-Lite, AXI, and AHB. This allows connectivity across varied IP blocks and processor architectures, including Arm, RISC-V, and x86. The technology’s topology-agnostic design enables customized NoC interconnect topologies, such as mesh and tree configurations, facilitating adaptability to specific application requirements and design constraints.

Designers can refine these topologies at key design stages, balancing automation with manual adjustments. This flexibility allows teams to meet performance objectives and application requirements while maintaining efficiency throughout the development process.

Reliability Considerations

As NoCs evolve, the need for reliability and functional safety continues to increase, especially in automotive and industrial applications where system failures could be fatal. Automation extends beyond efficiency, ensuring designers meet stringent safety standards while preserving performance and effectively managing resources.

To address these requirements, FlexGen incorporates hardware-based safety features that support ISO 26262 compliance up to ASIL D. With these capabilities, semiconductor companies can develop safety-critical applications that adhere to industry standards while maintaining performance, power efficiency, and reliability.

Next-Gen NoC Advancements

FlexGen smart NoC IP is a transformative technology that automates NoC design, enabling designers to manage growing chip complexity effectively. As AI and machine learning workloads surge, the global SoC market is projected to experience significant growth over the coming years. This growth emphasizes the need for robust, scalable NoC solutions to manage rising computational demands efficiently.

FlexGen from Arteris equips designers to align with emerging technologies and capitalize on market opportunities across high-growth sectors, including AI-driven automotive systems and edge IoT. The technology enables effective real-time decision-making, empowering designers to respond rapidly to dynamic market demands. As a result, the product sets new benchmarks for agility, productivity, and competitiveness in the semiconductor industry.

Learn more about how automation is transforming NoC design. Download the white paper here.

![]() Andy Nightingale, VP of product management and marketing at Arteris, has over 37 years of experience in the high-tech industry, including 23 years in various engineering and product management positions at Arm.

Andy Nightingale, VP of product management and marketing at Arteris, has over 37 years of experience in the high-tech industry, including 23 years in various engineering and product management positions at Arm.