As semiconductor applications continue to diversify, the traditional one-size-fits-all processor model is becoming increasingly outdated. Today’s designs demand greater specialization to meet the unique performance, power, and cost requirements of specific workloads. RISC-V, with its open-standard architecture and flexible customization model, has emerged as the ideal platform to address this shift.

Unlike fixed-ISA alternatives, RISC-V enables developers to create domain-specific processors for their systems-on-chip (SoCs). Custom instructions can boost throughput, reduce energy consumption, and shrink silicon area, all while preserving software compatibility and ecosystem portability. RISC-V’s open nature also reduces vendor lock-in, enabling faster innovation across automotive, AI, security, and high-performance computing (HPC).

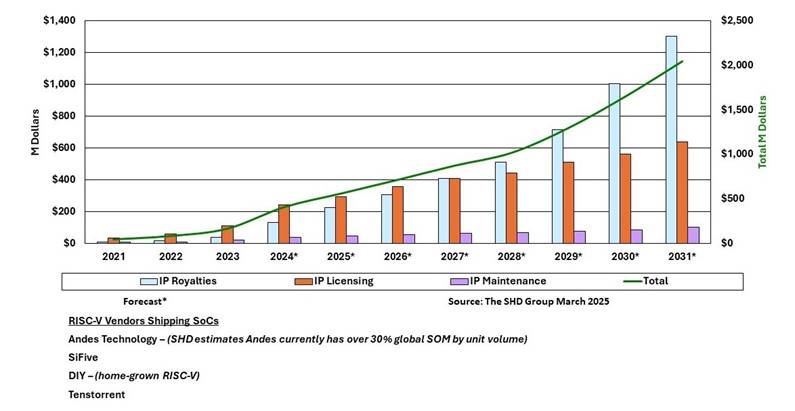

Andes Technology, a Founding Premier Member of RISC-V International, has been at the forefront of this movement. According to Rich Wawrzyniak, Principal Analyst at The SHD Group, Andes’ semiconductor intellectual property (SIP) is deployed in more than 30% of all RISC-V SoCs shipped worldwide, as shown below in Figure 1, underscoring its credibility as a trusted, production-proven solution.

Figure 1. RISC-V market revenue forecast through 2031. (Source: Rich Wawrzyniak, Principal Analyst, The SHD Group)

Application-Specific Performance with Andes IP and ACE

Andes offers a broad portfolio of 30+ silicon-proven processor IP cores, spanning compact 32-bit MCUs to high-performance 64-bit out-of-order CPUs. These cores are deployed in a wide range of applications, from IoT and consumer devices to communications infrastructure to AI acceleration in data centers.

At the heart of Andes’ customization capabilities is Andes Custom Extension™ (ACE), a native feature that enables developers to design and integrate custom instructions directly into the processor. Unlike bolt-on approaches, ACE is embedded in the architecture itself. This allows customers to insert specialized compute logic into the processor pipeline to accelerate targeted workloads while maintaining architectural correctness and implementation integrity.

ACE supports an expansive range of customizations. A simple extension might fuse common instruction sequences into a single ACE instruction to improve performance and reduce code size. More advanced extensions can define new register files, datatypes, and operations to implement domain-specific ISAs. Designers can even integrate low-latency, high-bandwidth interfaces that connect directly to traditional hardware accelerators, thus avoiding the performance and power penalties of traditional bus structures.

Automating Customization: ACE and CoPilot

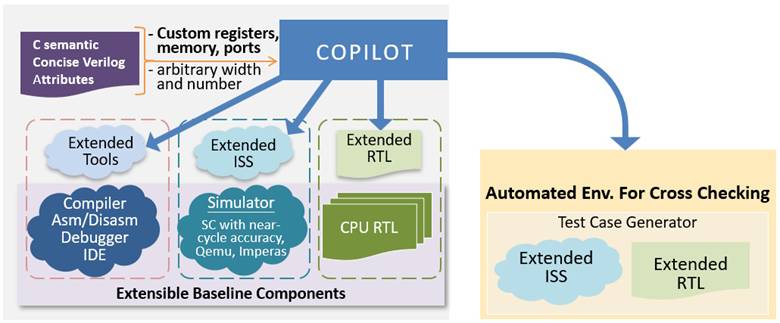

Once instruction extensions and processor customizations are specified in ACE, Andes CoPilot automates their implementation.

CoPilot is an intelligent automation tool that guides users through the process of defining, verifying, and deploying ACE instructions. It replaces the traditionally manual and error-prone steps by auto-generating the corresponding RTL, compiler and assembler support, debugger integration, simulation models, and IDE plugins, all from a single ACE specification, as shown in Figure 2 below. This automation makes custom instructions immediately usable across the full hardware and software stack.

Figure 2. ACE & CoPilot automate custom instruction development (Source: Andes Technology)

Together, ACE and CoPilot empower teams to innovate quickly, safely, and confidently at the instruction level and achieve true hardware/software co-design. Whether optimizing for performance-per-watt in a constrained embedded system or adding acceleration to a high-end AI inference engine, developers can tailor their processor with confidence.

Real-World Innovation

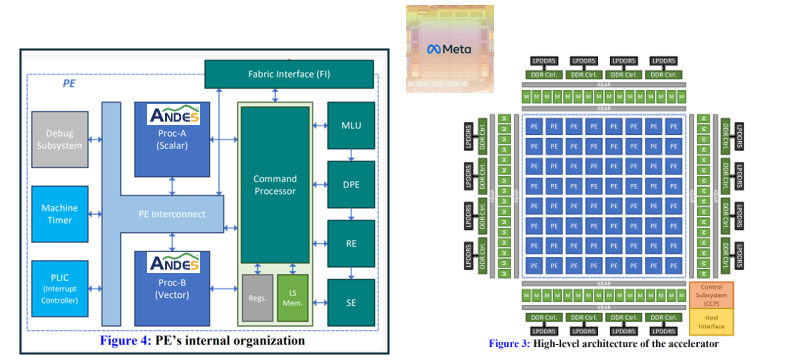

Leading tech companies are putting Andes’ tools to work in production silicon. Meta integrates Andes processors with numerous ACE-defined instructions into its MTIA (Meta Training and Inference Accelerator) chip, as referenced in Figure 3 below.

Figure 3. Source: ISCA 2023, “MTIA: First Generation Silicon Targeting Meta’s Recommendation Systems” - Amin Firoozshahian, et. al.

Figure 3. Source: ISCA 2023, “MTIA: First Generation Silicon Targeting Meta’s Recommendation Systems” - Amin Firoozshahian, et. al.

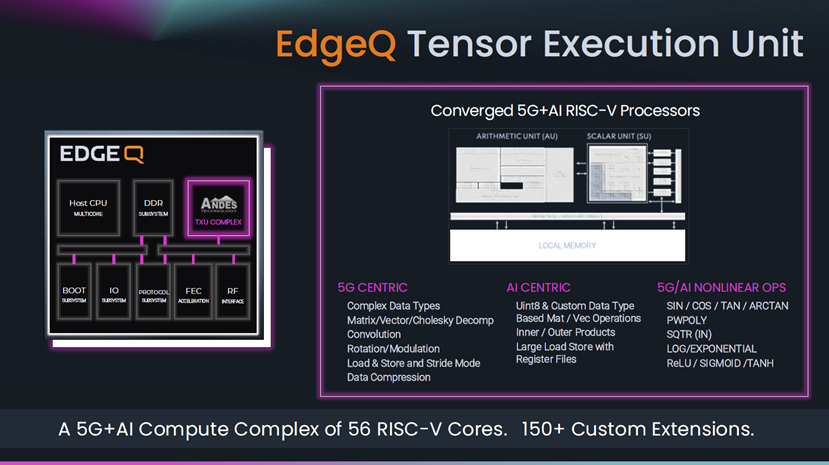

EdgeQ uses Andes IP in its 5G+AI Base Station-on-a-Chip, implementing a full 5G Software Defined Radio (SDR) with much of the baseband signal processing executed through ACE-defined extensions, as referenced in Figure 4 below.

Figure 4. EdgeQ integrates 150+ custom extensions in its 5G+AI Base Station-on-a-Chip. (Source: Andes Technology)

Over 75% of Andes customers internally create their own instruction extensions using ACE and CoPilot. This allows them to retain full IP control, protect proprietary innovation, and reduce external dependencies.

Customization as a Strategic Advantage

With ACE and CoPilot, the ISA flexibility offered by RISC-V is now a strategic enabler for next-generation chip design. Andes, now celebrating its 20th anniversary, is the only public pure-play RISC-V IP provider. Its proven architecture, mature toolchain, and robust support infrastructure make it a preferred partner for everything from real-time sensor hubs to high-performance compute-class SoCs.

Unlike processor IPs that don’t allow customization or restrict it behind proprietary tools and consulting services, Andes empowers customers to innovate independently. Its IP portfolio offers the configurability and automation required to optimize and extend RISC-V with confidence.

As the semiconductor industry shifts towards hyper-specialized design, RISC-V is the right ISA at the right time. Andes Technology is proud to support this transformation with the tools, IP, ecosystem, and support needed to deliver a customized and differentiated product.

Ready to Customize RISC-V for Your Workload?

Unlock performance, reduce power, and differentiate your SoC with Andes IP, ACE, and CoPilot. Learn more at www.andestech.com.

Author: Marc Evans, Director of Business Development & Marketing, Andes Technology USA

Marc is a proven semiconductor executive with expertise in CPU and DSP IP and SoC. At Andes Technology USA, he leads branding, go-to-market strategy, and strategic partnerships for Andes and its high-performance RISC-V subsidiary, Condor Computing. His background combines design engineering with strategic business development and market execution. Previously, he held key positions at CEVA and Tensilica, where he drove IP adoption across top-tier accounts and expanded into new markets.