By Darshan Bhuva, eInfochips

Abstract:

As the semiconductor industry is rapidly changing, there is limited margin of error for Designers, verification engineers and layout designers. We must get success on first cut as the Designing, Verification and Fabrication of chip is costly and time to market is tighten. It is difficult to get success in the first cut until we have a proper methodology to perform the whole ASIC development cycle. This ASIC development cycle requires human effort as well as tools like electronic design automation (EDA) which together can help in creating success stories. If we are talking about SoC Development, then it is better to get ready IP by some IP provider to make the process faster. Here we address the ASIC Physical Design Development cycle with respect to IP Implementation.

Introduction:

ASIC Design is ever-changing and ever-challenging. The key factor with long-existing challenges are high cost (for designing, verification, fabrication), tight deadlines, competition, complexity in design and verification of the product [1]. As the Technology shrinks from a higher node (i.e., 180nm) to lower node (i.e. 7nm) the complexity increases. According to Moore’s law, the transistors in a dense integrated circuit are double about every two years [2] to search for more computational power and capacity [1].

To overcome the challenges, proper methodology is required with the relative tools and flows. ASIC journey starts with user requirements (specification) and it tends to Fabrication (Tape out). This journey can be long with many critical tasks. Failure in any of the tasks results in chip failure. Even re-spin of the chip is also much costly and can affect business continuity. Therefore, we need a well-defined flow which helps us to achieve first-time success from specification to tape-out.

Other factors that contribute to chip failure are human error, immature EDA tools, lack of experience and discipline [1].

ASIC FLOW:

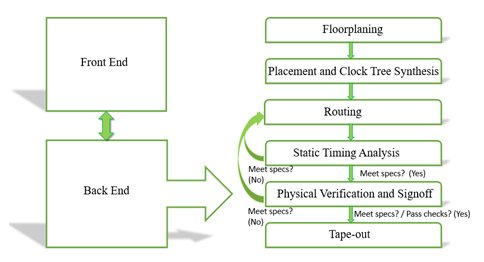

The ASIC flow can be divided into two parts: front-end and backend. Front-end includes (system specification) RTL designing with the help of Verilog/VHDL language to the circuit design (design synthesis). The backend includes the journey from logical design to layout design; Floorplan to GDSII (Layout) with the help of EDA tools i.e. Innovus, Tempus, QRC, PVS, etc.

In this paper, we will discuss backend flow with a flavor of IP Hardening.

Back-End ASIC Design Flow

- Backend (PD) flow

The backend includes the below steps which designers need to follow:

Floorplan, Power Planning, Placement, Clock Tree Synthesis (CTS), Routing, RC Extraction, Static Timing Analysis (STA), Power Analysis (includes EM/IR), Physical verification (include DRC, LVS).

- ASIC Challenges in terms of IP Hardening.

IP Hardening is complex to implement as it works on high frequency and contains multi-voltage domains. There might be a chance that it will be placed in such a design where voltage is different, so implementation should properly be guided and pass every required check. For Methodology, mature tools must be used which are mentioned below,

- Tools Required: Innovus / ICC2 (for Floorplan to Route), QRC / StarRC (for RC Extraction), Tempus / Prime Time (for Static Timing Analysis), Voltus / Redhawk (Power Analysis), PVS / Caliber (for Physical Verification like DRC, LVS).

- For effective work in IP implementation, people requirement depends on work and requirements. IP Work can be divided accordingly. i.e. one person is working on Floorplan, one is working on CTSlike , likewise.

- Challenges

- The most Challenging part of IP Hardening is proper Floorplanning (To minimize the skew and DRC), Skew fixing, Timing closure for critical paths, DRC fixing, etc.

- Floorplanning: If we complete the floorplanning effectively, we can improve skew, timing, DRC. There are many checks based on the design specifications, which we have to take care of. Now the question is what should be done in the floorplan? So, the answer is,

- We have to place macros and standard cells to get better timing and minimal skew violations. We need to define precise skew groups to achieve better skew.

- All macros and standard cells should be placed on-grid, failure of this will come up with base layer violations. Some tools take care of this.

- As skew is the major factor, here. We placed some clock cells in the floorplan itself by using tool commands or by manually adding clock cells so that the tool balances the skew. And Route them in floorplan with don’t touch attributes.

- The child module should be placed in such a way that its rows align and map with the parent module.

- Power Planning: Power Planning should be done in such a way that all the cells of design should get the proper power.

In IP we have multiple voltages for many cells for that, we have to customize the structure accordingly. The power net pattern should be VDD-VSS-VDD-VSS likewise. If multi-voltage is there than a pattern should be VDD1-VSS-VDD2-VSS likewise. Power straps of the child modules should be aligned and mapped with the parent module.

- Placement: The PnR tool has the ability to do a good placement of cells by performing an interactive process to improve WNS, TNS, DRV, and Congestion. By applying some control switches, we can optimize the timing, congestion, etc. we can specify the cell padding around high switching cells, which can help us to prevent IR issue.

After placement, we should check the placement whether any cells are placed off-grid or not? Are there any unplaced cells or not? EDA tool will place all the cells in the design at this stage so it should not have any unplaced cells (which are coming from netlist) after this stage.

- CTS: In IP, if we have built a clock tree at the floorplan stage to skew balancing for some of the critical paths, then we can get benefit in this stage.

In this stage, we have defined the clock root pins from which tool builds the clock tree. Also, we defined the skew groups and some other properties (i.e. NDR, Top/Bot Layers).

- ROUTE: In this stage, the tool routes the whole design with its algorithm by honoring manually applied constraints by the user. In this stage, tool will try to optimize the DRV, WNS, TNS, and Design Rule Checks (DRC).

- RDL Routing: If the block includes bump then we have to do RDL routing for it. We need to follow some instructions for RDL routing like, nets should be routed at 45° angle. No VIA should be dropped on BUMP. It should meet the requirement of spacing between net and bump, failure of which leads to DRC violations.

- Static Timing Analysis (STA): In this stage, we have to do some ECOs by analyzing timing reports. If required, we have to go back and change the floorplan as well to meet critical paths timing closure. Until and unless we have waivers and explanation for waiver, we have to meet timing at 0ps.

As per the skew reports and depends on rise/fall timing of cells we have to fix the skewing. By swapping or by adding buffers/Inverters.

- Power Analysis (EM / IR): In Power analysis, we generally check Power and Signal EM, Static and Dynamic IR. Static IR drop is voltage drop when constant current flow through the power network with varying resistance. But in real scenario circuit is not drawing constant current as many cells are switching in circuit hence Dynamic voltage drop comes into the picture. Due to the High current flow in metal layers atoms are displaced from its original place hence large amount of metal can open or bulging of metal can happen this effect is called Electro Migration (EM).

We have solved this EM violation which was mostly on clock nets by increasing the area of the metal as we had other options due to other critical issues. e.g. We had some critical timing paths for which we cannot add buffers or clone the clock cells because it will again come up with the timing violations.

- Physical Verification: This stage consists of Design Rule Checks (DRC), Layout Vs Schematic checks (LVS), Electric Rule Checks (ERC), Resistance check (PERC). All the checks should go clean to send IP for the tape out.

In this part, we solved many metal DRCs in which Metal loop DRCs are hectic to solve as it occurs in layers with a double pattern. For base DRC fixing, we have applied some settings so that the tool can take care of filler cell placement in the cell gap and also changed the orientation if needed.

Conclusion:

For faster time to market we require well defined and well-guided methodology. Human effort along with EDA tools plays a very important role. With multiple Iterations and proper analysis, we can improve the quality of the methodology in terms of Timing and DRCs.

Reference:

- https://www.intechopen.com/books/application-specific-integrated-circuits-technologies-digital-systems-and-design-methodologies/case-study-first-time-success-asic-design-methodology-applied-to-a-multi-processor-system-on-chip

- https://en.wikipedia.org/wiki/MooreHYPERLINK "https://en.wikipedia.org/wiki/Moore's_law"'HYPERLINK "https://en.wikipedia.org/wiki/Moore's_law"s_law

- https://en.wikipedia.org/wiki/Physical_design_(electronics)