By Agnisys

Introduction

System-on-chip (SoC) designers face significant challenges when integrating thousands of IP blocks from various vendors, often presented in different formats. The manual stitching and debugging of these components can result in quality issues, extended time-to-market (TTM), and complex integration hurdles. As designs grow more complex, the necessity for validation of connectivity, and adherence to IP-XACT standards, becomes increasingly crucial.

Introducing IDS-Integrate

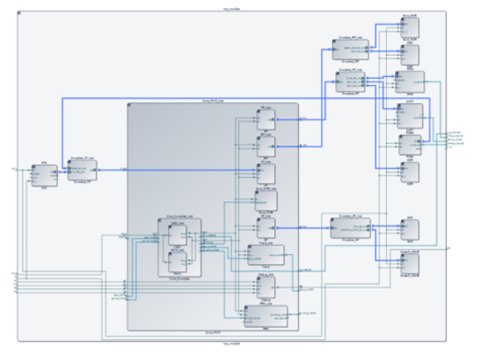

IDS-Integrate is designed to tackle these challenges by automating the assembly and packaging of numerous IP blocks, including third-party options, into cohesive SoC designs. This powerful tool simplifies the integration process for IP-XACT (IEEE 1685-2009, 2014, and 2022) and RTL (Verilog, SystemVerilog) formats, enabling designers to automatically generate high-quality outputs such as RTL, IP-XACT files, documentation, assertions, graphical views, and C/C++ headers.

The versatile Tcl and Python APIs facilitate connectivity specifications, enabling automatic connections between initiators, targets, drivers, receivers, clocks, resets, and ports along with the capability of regular expression usage. It also supports features such as hierarchy partitioning and flattening, allowing seamless restructuring of components across projects. Built-in design rule checks validate connectivity before generating outputs, ensuring compliance and reliability throughout the SoC design process.

Challenges and Use Cases for Automated Chip Assembly

Manually connecting hundreds or thousands of blocks into a top-level SoC design is a tedious and error-prone task. Designers often struggle with linking similar named signals, where typographical errors are almost inevitable. The repetitive process of hooking up multiple instantiations of the same block can be particularly frustrating. Typically, interconnection errors are detected late in the project, only when full-chip simulation is underway, making debugging difficult due to the design's complexity.

Agnisys addresses these challenges with IDS-Integrate, applying specification automation to SoC-level assembly and interconnection. This tool provides a flexible and customizable environment tailored to meet the specific design requirements for complete chips.

IDS-Integrate empowers designers by enabling use cases such as:

- Connecting tool generated blocks with your design blocks and creating a wrapper around it

- Reading an IP-XACT component and connecting it with existing blocks

- Connecting an AHB bus with an APB slave by automatically instantiating a bridge

- Connecting multiple AHB blocks to an AHB master through the automatic instantiation of an aggregator

- Moving a block from a deep hierarchy several levels higher

- Generating SystemVerilog Assertions (SVA) for connectivity checks using formal verification

With these capabilities, IDS-Integrate enhances development processes, ensuring high-quality designs while significantly reducing manual effort.

Features and Benefits

By automating the generation of integrated outputs, the tool eliminates manual coding errors and automates integration. Connectivity is validated with built-in design rule checks and assertions, ensuring that all components function seamlessly together.

The tool supports the assembly of SoC designs with both custom IP blocks and commercial offerings. The automatically generated RTL includes synchronization logic for clock domain crossings (CDCs) necessary for connecting the IP with internal and external buses, along with required bus bridges, aggregators, or multiplexers.

Additionally, IDS-Integrate enables efficient management of arrays of instances of blocks through parameterized RTL and IP-XACT specifications via Tcl/Python APIs. It incorporates the TGI (Tight Generator Interface) API, enhancing integration capabilities with third-party vendor extensions. The latest features include support for power specifications in UPF (Unified Power Format), SDC (Standard Design Constraints), CDC specifications, and advanced Semantic Consistency Rules (SCR) for IP-XACT, which position IDS-Integrate as a forward-thinking solution. The addition of spreadsheet-based connectivity specifications further streamlines the design process, improving overall productivity and fostering innovation in SoC projects.

The Role of IP-XACT and IDS-Integrate

IDS-Integrate plays a pivotal role in streamlining the SoC design process. By automating the assembly, packaging, and catalog generation of numerous IP blocks, it enables designers to automatically generate high-quality outputs and ensure efficient restructuring of components. The tool supports the automatic connection of various elements while validating connectivity to guarantee compliance and reliability.

Conclusion

In conclusion, adopting IP-XACT and leveraging IDS-Integrate can significantly shorten the SoC development cycle. By standardizing data exchanges and automating critical processes, teams can streamline workflows, enhance collaboration, and accelerate time-to-market for their SoC designs. This approach not only improves efficiency but also enhances the quality and reliability of the final product, paving the way for innovation in the semiconductor industry.