In today’s fast-paced silicon industry, hardware design is under constant pressure to innovate, iterate, and ship faster. Traditional Register Transfer Level (RTL) design processes—though foundational—are time-consuming, error-prone, and heavily reliant on manual expertise. With growing design complexity and shrinking time-to-market, the need for automation in digital design is more critical than ever.

This is where Artificial Intelligence, particularly Large Language Models (LLMs), is making waves. More specifically, Agentic AI – a system composed of multiple autonomous agents powered by LLMs – offers a way to automate RTL design through intelligent, feedback decision making, rather than static prompt-based output.

The Need for AI in RTL Design

RTL coding involves describing the behavior and structure of digital circuits using hardware description languages (HDLs) like Verilog or VHDL. It's the backbone of ASIC and FPGA design flows. However, RTL development remains a bottleneck in hardware projects due to:

- Human dependency: Only experienced engineers can efficiently write optimized RTL.

- Error-prone syntax: Small mistakes can break functionality or delay verification.

- Manual iterations: Debugging, testbench creation, and simulation are repetitive and tedious.

Enter AI-powered code generation. Much like how LLMs revolutionized software development with tools like GitHub Copilot, there’s a growing trend to apply similar intelligence to HDL generation. But can LLMs truly understand and automate RTL workflows?

How LLMs Are Used in RTL Code Generation

Modern LLMs like Code Llama, DeepSeek-Coder, Mistral, and Gemini Code are already being experimented with for HDL generation. Their ability to understand prompt-driven instructions and generate syntactically correct Verilog/VHDL is impressive. Use cases include:

- Converting functional specifications into RTL

- Translating English to Verilog

- Creating simple state machines or arithmetic units

- Autocompleting partial designs

However, these models often operate in isolation, generating code without feedback, unaware of simulation failures, and unable to debug their output.

Why LLMs Alone Are Not Enough

Despite their strengths, standalone LLMs fall short when it comes to the end-to-end RTL lifecycle. They struggle with:

- Context retention across long generation chains

- Error recovery after testbench simulation failures

- Semantic validation, like signal mismatches or edge-case coverage

- Feedback learning during iterative design debugging

In short, while LLMs can write code, they lack autonomy and adaptability, both essential in real-world RTL development.

This is where Agentic AI offers a transformative solution.

Introducing Agentic RTL Coder at MosChip.

MosChip has developed a module, a multi-agent architecture powered by LLMs that simulates the decision-making process of an expert RTL designer. Unlike a single LLM that acts once, Agentic AI involves a feedback-driven agentic loop, allowing the system to evaluate, refine, and regenerate RTL code until the final output passes all simulations.

Core Components of the Agentic Architecture

Here’s how the system works:

1. Prompt Enhancer Agent:

Refines the user’s natural language input into a technically complete and unambiguous specification.

2. RTL Generator Agent:

Uses an LLM (like DeepSeek-Coder or Llama3) to generate RTL code based on the enhanced prompt.

3. Verilator Lint Agent:

Performs static linting using Verilator to catch syntax and style issues.

4. Testbench Generator Agent:

Extracts module headers and generates a full testbench using the same or another LLM.

5. Simulator Agent:

Compiles the RTL and test bench using Icarus Verilog and executes the test bench to verify functionality.

6. Trackback Mechanism:

If the simulation fails, the system tracks which file (RTL or TB) causes the issue and invokes the corresponding agent to regenerate the output.

Each agent operates autonomously but cooperatively through a LangGraph-based control flow that maintains state, memory, and retry logic.

Comparing LLMs for RTL Generation

|

Model Name |

Strengths |

Limitations |

|

Code Llama |

Fast generation, good syntax |

Weak on testbench or FSM logic |

|

DeepSeek-Coder |

Strong Verilog-specific output |

Limited debugging context |

|

Gemini Code |

Broad understanding of digital design |

Slower and not fine-tuned for Verilog |

|

Mistral 7B |

Lightweight, accurate |

Not domain-optimized |

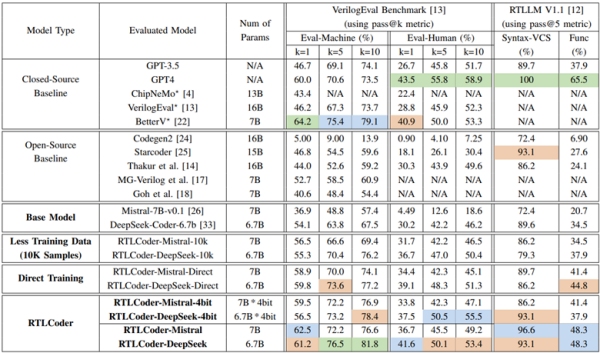

MosChip’s Agentic RTL Coder adopts a dual-model strategy to balance design quality and processing efficiency. DeepSeek-Coder is chosen for RTL and testbench generation, paired with Llama3 for prompt enhancement. The dual-model setup ensures high-quality design and robust error resolution.

Reference: Link

Time & Productivity Gains

|

Task |

Traditional RTL Flow |

Agentic AI Flow |

|

RTL generation |

1–2 hours |

~1–2 minutes |

|

Testbench development |

1–2 hours |

~1 minute |

|

Iterative bug fixing |

Manual, tedious |

Autonomous |

|

Overall turnaround (avg.) |

~4–6 hours |

~5–10 minutes |

Time saved: >90% for standard design blocks.

Impact: Enables rapid prototyping, design reuse, and scalability.

Challenges in Building Agentic RTL Systems

- Prompt ambiguity: Users often write vague prompts; agents must clarify intent.

- Simulation errors: Some errors are tool-specific (Icarus vs Verilator).

- Code hallucination: LLMs sometimes invent ports or mislabel signals.

- Infinite loops: Retry mechanisms with short-term memory were crucial to avoid cycles.

Conclusion

MosChip’s Agentic RTL Coder represents a significant evolution in the digital design landscape, shifting RTL development from a manual, linear task into a more intelligent, collaborative process. By leveraging a multi-agent architecture that incorporates feedback, refinement, and adaptability, the system redefines how engineers interact with design tools.

Agentic AI isn’t here to replace RTL engineers—it’s here to empower them, automating the tedious so they can focus on architecture, optimization, and innovation.

The future of hardware design is not just automated. It's agentic.

MosChip® supports smarter, faster chip design with AI. The Agentic RTL Coder brings together the power of Large Language Models (LLMs) and a multi-agent architecture to automate RTL generation, testbench creation, and simulation, all in a seamless, feedback-driven loop.

By combining multiple models with industry tools such as Verilator and Icarus Verilog, the system produces clean, simulation-ready Verilog while handling lint checks, bug tracking, and regeneration automatically.

Whether you are looking to speed up ASIC design, streamline FPGA workflows, or adopt AI for faster, smarter RTL development, MosChip’s Agentic RTL Coder is built to help you accelerate your silicon journey, reduce errors, and focus more on architecture and innovation, where it counts.