Why Combo DDR Still Matters

In today’s fast-paced SoC market, memory flexibility is no longer a luxury—it’s a competitive necessity. While DDR5 is gaining traction in high-performance systems, DDR3 and DDR4 remain dominant in embedded, industrial, and cost-sensitive markets. A combo DDR3/4 interface offers engineers a way to bridge these worlds, maximizing product reach while reducing design risk.

Design Challenges in Supporting Multiple DDR Standards

Supporting both DDR3 and DDR4 in a single subsystem is not as simple as connecting to two memory types. Engineers must address:

- Interface Protocol Differences – Command timing, initialization sequences, and training flows vary significantly between DDR generations.

- Signal Integrity & PHY Design – Maintaining eye margins across speed ranges from DDR3’s 2133Mbps to DDR4’s 3200Mbps requires precise PHY tuning, deskew, and baseline wander compensation.

- Power Optimization – Embedded applications often require aggressive low-power modes without sacrificing performance bursts.

- System Integration Complexity – Multiport memory controllers must handle mixed workloads, QoS arbitration, and ECC without bottlenecks.

Key Design Tips for a Flexible DDR Subsystem

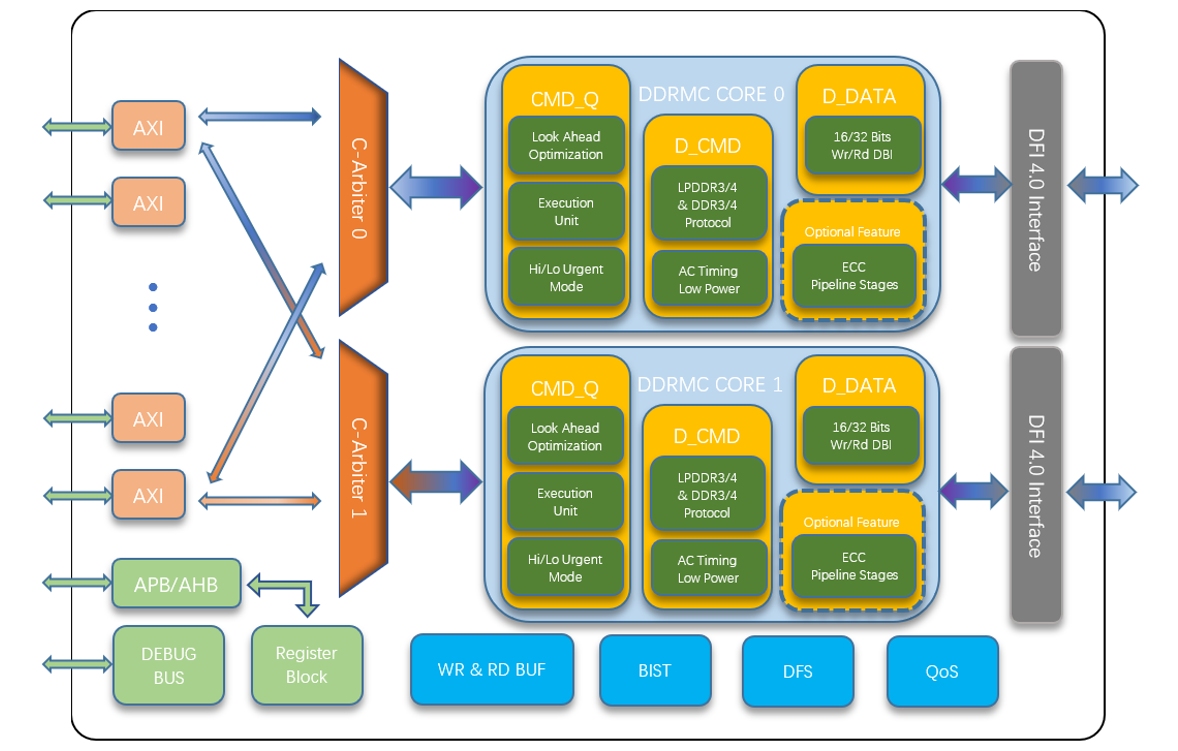

- Adopt a Configurable Controller Architecture

Use a memory controller with configurable AMBA AXI4 ports, adjustable FIFO depth, and flexible command queues. This ensures you can adapt to different SoC workloads without redesigning the memory interface. - Implement Robust PHY-Level Training

Eye training, write leveling, per-bit deskew, and VREF calibration are essential for maintaining timing margins, especially when switching between DDR3 and DDR4 modes. - Leverage Power-Aware Features

Hardware-based DDR frequency switching (DFS) and selective rank power-down modes can significantly cut idle power consumption, which is crucial for battery-powered medical or IoT devices. - Plan for ECC Early

For DDR4, ECC support (32/64-bit data + 8-bit ECC) helps meet reliability targets in automotive, networking, and industrial applications.

A Practical Example of the DDR3/4 Combo IP

Key ASIC’s TSMC 12nm DDR3/4 combo IP is an example of how a well-architected solution can simplify multi-standard design.

- Performance: DDR4 up to 3200Mbps, DDR3 up to 2133Mbps

- Integration: DFI 4.0 compliant PHY, multiport AXI4 controller

- Low Power: Automatic clock gating, DFS, per-rank power control

- Testability: Built-in self-test (BIST), loopback modes, SIPI/LFSR patterns

These capabilities allow SoC designers to target diverse markets with a single silicon design, reducing NRE costs and speeding time to market.

Designing for the Next Decade

Even as DDR5 adoption grows, DDR3 and DDR4 will remain relevant for years in many verticals. By implementing a combo DDR3/4 interface, SoC designers can build flexible, future-proof memory subsystems that meet the needs of today’s diverse applications—from high-end networking gear to embedded industrial controllers.

【About Key ASIC】

Key ASIC, listed on Bursa Malaysia (0143), is one of the world's leading turnkey ASIC design service companies, offering comprehensive support from design to chip production.

- Over 100 ASIC designs in mass production

- 100% successful ASIC tape out

- Over 150 silicon-proven IPs

As a foundry-independent company, we collaborate with top-tier foundries worldwide, providing unparalleled flexibility and expertise to meet our customers' diverse needs.

Key ASIC is here to provide the best partnership for your ASIC business.

Please feel free to contact us via email: info@keyasic.com