System-on-chip (SoC) design cycles are being reshaped as architectures scale in complexity, driven by AI/ML, high-performance computing, and automotive ADAS. Meeting the compute demands requires managing hundreds of IP blocks, often from multiple internal teams and trusted third-party providers, with absolute consistency from concept through production. Each block brings its own registers, address maps, and bus interfaces. As hardware and software teams increasingly work in parallel, any incomplete or inconsistent data can cause interoperability mismatches, extend debug cycles, and trigger costly late-stage rework.

To avoid these pitfalls, IP descriptions need to be clear. When structured and easy to exchange, they become a single source of truth allowing multi-disciplinary engineering teams to automatically generate error-free RTL netlists, drivers, register models, and verification collateral, keeping everything in sync. It also promotes IP reuse across projects and design derivatives. Additionally, downstream artifacts can now be regenerated, avoiding monotonous hand editing.

Standardizing this process enables a unified methodology for automation. To support this, the industry has embraced IEEE 1685 (IP-XACT), which provides a common, machine-readable IP schema that becomes the shared language between IP metadata and EDA tools, enabling interoperability. The latest version, released in 2022, improves design description accuracy and usability, highlighted below:

- Native SystemVerilog feature support for a more complete and straightforward representation of modern RTL.

- Enhanced connectivity to better capture and manage complex interconnect structures.

- Expanded memory object descriptions for richer representation of system interfaces.

- Better support of parameter propagation, including dependency expression, for more flexible and accurate configuration.

Automating IP-XACT for Accuracy and Efficiency

Arteris Magillem Packaging addresses the practical challenge of producing high-quality IP-XACT descriptions by automatically capturing HDL. It supports both full and incremental packaging, importing Verilog and SystemVerilog from file lists or directories, including mixed-language projects. FileSets are prepared for simulation, synthesis, emulation, and verification.

Static elaboration evaluates parameters, expands macros, interprets system or user-defined functions, and processes generate blocks before packaging. This ensures that IP-XACT output reflects the complete source design. Multi-abstraction level descriptions allow the same component to be represented for different tasks without duplication. Memory map intent can also be captured to define the hardware/software interface.

A built-in suite of Magillem IP-XACT checkers verifies syntax, structure, and semantics against the standard as well as best-practice rules. Severity levels can be configured, and waivers with contextual help allow exceptions without introducing inconsistencies. For legacy content, Magillem Packaging supports the 2009 and 2014 versions, converting them to the 2022 format. This preserves investment in existing IP.

A single IP-XACT description, organized into views, can support multiple stages of the design flow. Bus interface auto-mapping connects the bus protocol’s logical ports to the IP’s physical ports. The Tight Generator Interface (TGI) API enables scripted create/modify/query operations and integration with broader automation frameworks.

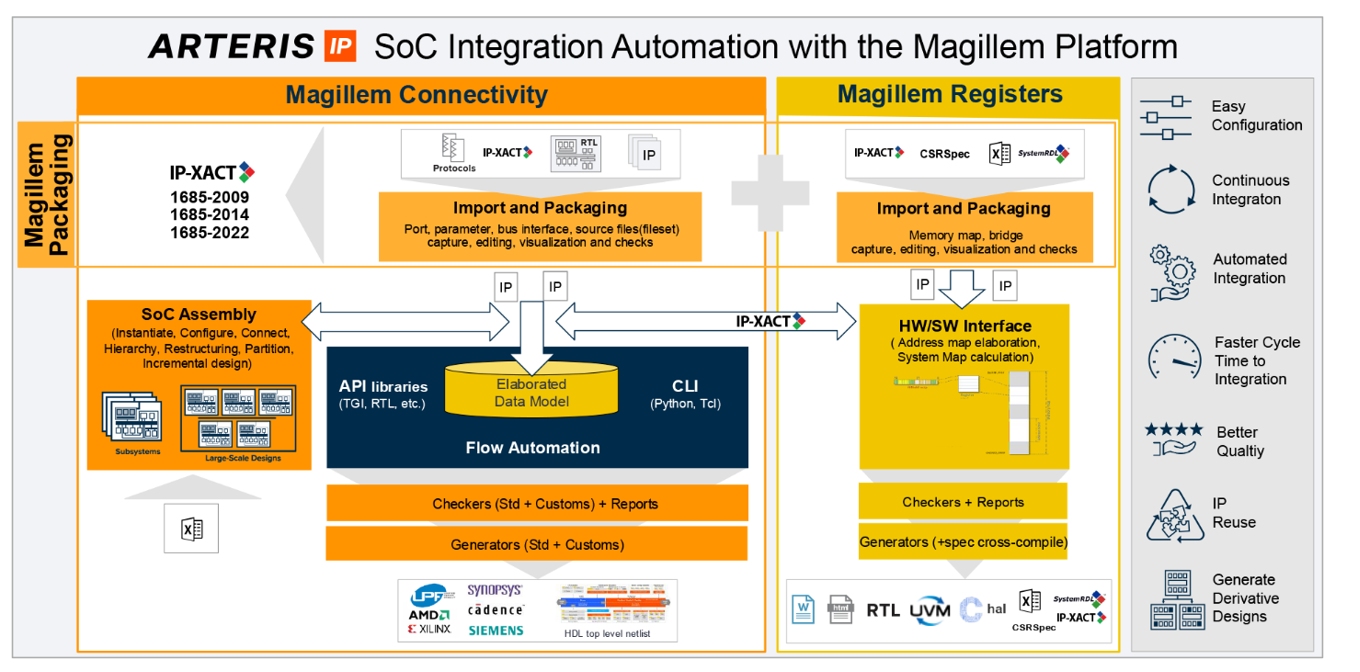

Figure 1. SoC Integration Automation with the Magillem Platform (Source: Arteris, Inc.)

Future-Ready SoC Integration

As SoC programs grow into heterogeneous platforms, IP integration is emerging as a key enabler of system-aware design, where early decisions made can influence later implementation stages. To stay ahead, solutions must evolve alongside architectural trends, supporting greater abstraction, faster iteration, and deeper alignment with system objectives. Whether targeting AI-driven SoCs, next-generation architectures, or scalable platform reuse, packaging plays a central role in enabling correct-by-construction design across diverse design domains.

Arteris addresses this challenge with a coordinated suite. Magillem Packaging establishes a reliable foundation for assembling, managing, and scaling complex IP across evolving SoCs. Magillem Connectivity captures hierarchical interconnect intent, enabling fast and safe system assembly based on consistent packaging of IPs, bus fabrics, and protocol interfaces. Magillem Registers provides a unified environment for specifying and managing control/status registers across hardware and software. Together, these tools form a cohesive framework that supports alignment across domains, improves design scalability, and equips engineering teams to manage growing architectural and organizational complexity.

About the Author

Insaf Meliane is a product management and marketing director at Arteris. Before joining the product team, she was a field application manager, supporting customers with complex SoC design integration. Before joining Arteris, she held other design and application engineering roles at leading semiconductor companies. Insaf holds an engineering degree in microelectronics option system-on-chips from Ecole Nationale Supérieure d’Electronique et de Radioélectricité de Grenoble.