Developing a system-on-chip (SoC) starts with the right building blocks: pre-designed, thoroughly tested IP modules for logic, memory, input/output (I/O), and other core functions.

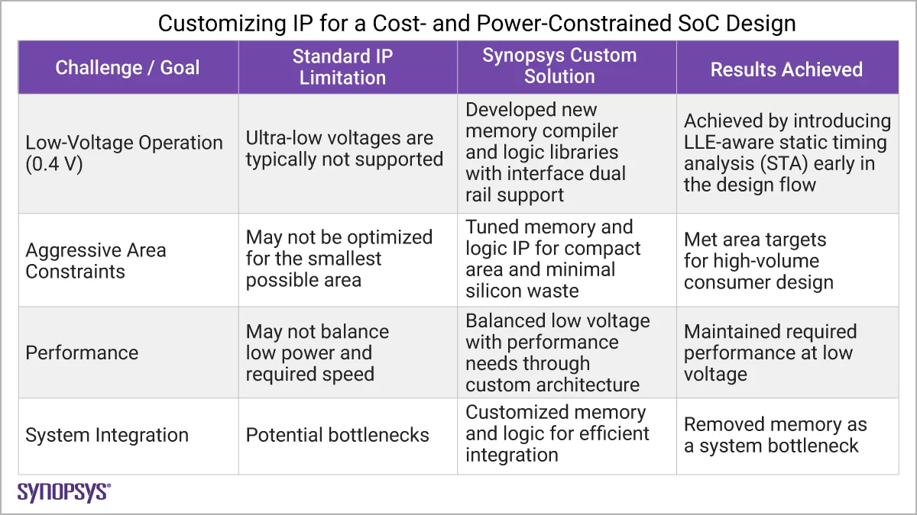

While standard IP offerings address most design requirements, some projects demand more — especially when innovation is the priority or when projects have aggressive power, performance, or area (PPA) targets.

As such, IP customization is becoming increasingly important.

This is where Synopsys truly stands apart. We don’t just offer the industry’s broadest portfolio of silicon-proven IP — we’re willing to go the extra mile to customize our IP solutions for specific customer needs.

Adapting Foundation IP for power-critical optical networking chips enabling AI at the Edge

One of our customers recently approached us with a unique situation and set of requirements. They wanted to develop a new chip to enable the optical network infrastructure supporting the surge in demand for Edge AI. The chip needed to perform reliably at just 0.4 volts and they couldn’t find IP solutions capable of supporting such low voltage. They also had an extremely aggressive, eight-month delivery timeline.

Always up for a challenge and backed by the industry’s most comprehensive, silicon-proven, application-enhanced, and adaptable portfolio of Foundation IP, our team quickly jumped into action.

Innovating memory design to enable lower voltage operation

Following a thorough evaluation of the customer’s PPA targets, it was clear the low-voltage requirements of the design would prove challenging for both memory compilers and logic libraries.

Memory bit cells — tiny storage elements within a chip — are typically unreliable at 0.5 volts or less. To solve this problem, our team developed a new memory compiler architecture. They refined the bit cell design, adjusted peripheral circuitry, and used advanced low-leakage transistors to ensure stability at lower voltages.

For other memory types, our team enhanced dual rail support — preferred for this technology node — which allowed different parts of the chip to operate at different voltages. Memory arrays, for example, typically need a higher minimum operating voltage than logic circuits. Our dual rail support enhancements ensured the logic circuits would not be restricted by memory voltage requirements. This flexibility helped minimize power across the entire chip.

Enhancing silicon utilization and optimizing power efficiency

In addition to enabling low-voltage operation, our team helped minimize the silicon area of the design while maximizing power efficiency. This included:

- Optimizing the memory architecture to occupy less space.

- Customizing logic components with smaller, more efficient building blocks.

- Implementing power gating techniques and low-leakage cell libraries to reduce energy consumption during idle periods.

- Utilizing advanced manufacturing technologies to fit more functions in a smaller space.

Together, these enhancements enabled every part of the chip to consume less power and occupy less space — crucial benefits for the cost- and power-constrained systems the chips will support.

Meeting all PPA, reliability, and delivery targets

Once the customer’s efficiency goals were met, our team developed a silicon test chip to validate the custom memory compiler and ensure real-world robustness. Comprehensive stress tests and benchmarks confirmed performance and stability, helping address issues early and build confidence in long-term reliability.

The design not only achieved all PPA targets — it was also completed within the customer’s demanding eight-month project timeline. The chip is currently pending tapeout, with production anticipated to follow.

Unmatched IP customization and collaboration

Customizing IP modules is no easy feat, especially when aggressive PPA targets and condensed delivery timelines are involved. It requires close collaboration, design and engineering flexibility, and a willingness to tackle deep technical challenges — a level of engagement most IP providers are unwilling to provide.

Synopsys is different.

With the industry’s most comprehensive and adaptable Foundation IP portfolio, a world-class R&D engine, and a highly collaborative team of field engineers, we stand ready to help customers overcome complex technical challenges and achieve their most ambitious PPA goals.