Where in the JESD world is bitstream alignment?

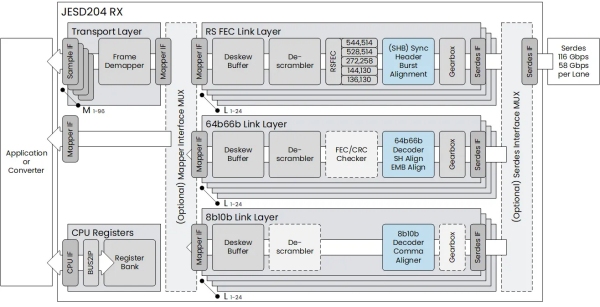

Bitstream alignment is a function of the Receiver (RX), as seen in the figure below it is the first functional block of the receiver right after the clock domain crossing (CDC) and gear boxing which are quite generic Serdes adaptation layer that can be found in almost every design working with a Serdes. In each iteration of the JESD204 standard this block is called a different name (Comma alignment, SH alignment, SHB alignment) but they serve the same purpose; to orient the receiver to where the decoding boundary is, and on which bit of the parallel data of the Serdes it should start interpreting data.

Why do we need bitstream alignment

The JESD204 Standard employs High Speed Serdes blocks to sends parallel data across serial lanes. In doing so the receiver of such serial data faces a challenge to identify where data boundaries lie withing the bit stream. As the receiving Serdes locks to any one of the many bits in the bit stream often the presented parallel data is shifted compared to the transmitted original with the receiver observing a later part of one word concatenated with the earlier part of the next. Without proper bitstream alignment, decoding the data through the Link Layer Datapath becomes impossible with the decoders descramblers and other functions relying on proper bit alignment. Each encoding method achieves the bitstream alignment in its own unique way, but all face the same objective, to align the data to the same boundaries as it was presented to the Serdes from the transmitter. This in fact is the first step for proper decoding in the Link Layer.

8b10b encoding – Finding the K28.5 characters

In JESD204, JESD204A and JESD204B the receiver (RX) and transmitter (TX) perform a handshaking operation with the use of the sync_b signal, with the RX instructing the transmitter to send first a constant stream of Comma Characters with the code of K28.5 while sync_b is being requested (held low), followed by the Initial Lane Alignment Sequence (ILAS), once the word boundaries have been established, and sync_b is released (released high).

While requesting sync the RX will perform a bit shift operation to find the proper alignment to the K28.5 (0xBC) characters and it can achieve this thanks to the special encoding the character carries. K28.5 is represented as K28.5+ 110000_0101 and K28.5- 001111_1010 depending on the running disparity and as the pattern contains a sequence of either 5 consecutive 1’s or 0’s it allows the RX to uniquely identify which bit is the first bit of the word. The fact that there is a 6:4 1’s and 0’s encoded will cause the disparity to toggle on each character, which makes the pattern placement even more relevant for proper character boundary identification. Once the boundary is identified a simple bit shift operation allows the data to be aligned to the rest of the receive data path.

64b66b encoding – Searching for the Sync Header pair

In JESD204C a new encoding scheme has been deployed one in which the 64-bit blocks are not actually encoded but 2 additional bits are appended allowing the demarcation of the block boundaries. The content of the blocks is scrambled within the transmit (TX) data path and due to this there are not constant patterns of 1’s or 0’s withing the data section of the block to allow for alignment. The 2 extra bits of the 64b + 2b = 66b encoding called the Sync Header (SH) are omitted in the scrambling processes and hold a unique value of 10 or 01. This special constraint serves two purposes, the first being bitstream alignment allowing for the Self Synchronizing Receiver to easily, by process of elimination, identify the block boundaries, and the second purpose allowing the bits to represent a value of 0 or 1 when forming a 32 bit Sync Header Word for carrying Multi Block Synchronization information, Cyclic Redundancy Check data, Fire Code Forward Error Correction Data, or even the Command Channel data. The selected values of 10 or 01 rather than 11 or 00 maintain the DC balance and prevent baseline wander as well as aiding in clock data recovery (CDR).

In the 64b66b encoding scheme the receiver is called “self-synchronizing” since it no longer needs to rely on a handshaking mechanism between the TX and RX to allow for the synchronization to happen. The transmitter (TX) can simply transmit data without any concern for the state of the receiver (RX), and since the synchronization data is embedded in the appended SH bits continuously the receiver can start observing the bit stream and perform alignment without the TX knowing. Similarly in an error situation the RX can perform unassisted realignment without disturbing the TX. This allows for removing the sync_b pin between the TX and RX entirely allowing for a simpler interface, the only drawback is subclass 2 for deterministic latency can no longer be supported.

RS FEC encoding – The fixed pattern of the Sync Header Burst

In JESD204D the concept of Sync Header bits has been taken a step further introducing Sync Header Bursts (SHB)1, which are effectively groupings of Sync Header bits instead of having them be dispersed between blocks. The SHBs are placed between FEC Code Words which are significantly larger than 64bit blocks of 204C, for example in the case of RS(544,514) FEC the codeword is 5440 bits long, in this case however the SHB contains multiple bits grouped together. Despite appearing less frequent they serve the same purpose, containing a fixed pattern they allow the Receiver to identify FEC Code Word boundaries and properly align the bitstream.

The SHB is composed of 10 bits and inserted in between every transmitted FEC Codeword. The 10 bits contain a constant pattern that can be identified by the RX in the scrambled bitstream. The value is organized in such a way to always contain five values of 1 and five values of 0. this way similarly to 64b66b encoding DC balance is maintained to prevent baseline wander as well as well as aiding in clock data recovery (CDR). The receiver is also “self-synchronizing” not requiring any additional handshaking from the transmitter.

1 In the final specification the Sync Header Burst (SHB) is named Sync Header, however I choose to maintain the “Burst” designation from early JEDEC TG16 committee discussions to differentiate between 64b66b 2-bit sync headers and RS FEC 10-bit sync headers.

Design Guide: Why is my RX not Locking?

When you are experiencing your RX design dropping SH LOCK status or not obtaining it at all the first thing to check would be Serdes Line Rate configuration and if the Serdes is obtaining proper CDR lock, indicating Serdes Link up. Any bit slipping in the Serdes would effectively change the bitstream alignment and cause the design to lose SH LOCK. With that being stable the next item to check is the frequency relationship between the Serdes clock domain and Character/Core clock domain. In a multi lane design there will be individual recovered clock domains for each Serdes Lane, and these are most often Clock domain crossed into the Link Layers clock domain. In situations where deterministic latency is required these could be clocked by an external clock aligned with SYSREF. Any drift present between these 2 clock domains can eventually lead to the CDC crossing buffer to underflow/overflow leading to loss of data and effectively any Serdes to Data bus Gearbox established position changing, and in result the synch header location also shifting. Clocking is one of the main reasons for not obtaining or periodically losing the SH LOCK.

Another common reason you could be experiencing not being able to SH LOCK is the wrong ordering of Serdes bits. Some Serdes vendors will provide LSB first other MSB first on the parallel interface of their Serdes proper orienting the data before passing it to the Gearbox and Clock Domain crossing elements is crucial for the bits appearing in sequence and SH lock to be possible. Please check your providers interface declaration matches the expected order on the JESD interface. Chip Interfaces JESD204 IP core implements a reversal mechanism to allow for correcting for this oversight even in post tape out scenarios.