As regular readers know, at Agnisys we offer our IDesignSpec Suite of products to automate the design, verification, programming, integration, validation, and documentation of your IP and system-on-chip (SoC) designs. Usually I start a post with a known challenge in chip development, explain how specification automation solves or greatly diminishes that challenge, and let you know which of our products are relevant. Today I’d like to turn this around by assuming that you’re considering our solutions and by offering five strong reasons for you to choose us.

Memory Map Design

Today’s processors have very large memory spaces containing addresses ranges allocated for different types of memories and a huge variety of registers. Control and status registers (CSRs) are a key part of the hardware-software interface (HSI). They allow low-level software such as drivers, microcode, and embedded programs to configure the SoC hardware and read back status. Tens of thousands of CSRs, containing complex sets of bits and fields, are common in today’s chips. Designing the memory map with all the address assignments and register details is a major task.

Our IDesignSpec GDI and IDS-Batch CLI tools automate the design of your registers and memories. You can specify your memory map using standard formats such as SystemRDL and IP-XACT, import Excel spreadsheets, or use our intuitive interactive editor (IDS-NG). We generate the register-transfer-level (RTL) design for your registers and memories, along with high-quality documentation. In addition, our IDS-Verify tool generates a Universal Verification Methodology (UVM) testbench and tests. We automatically regenerate all files whenever you make any changes to your memory map specification.

CPU Access

CSRs, as part of the HSI, must be accessible from the CPU(s) in the system. IDesignSpec helps you in two ways. First, when we generate the RTL design for the registers and memories we also generate the interface to the CPU bus. We support many standards, including APB, AHB, AHB-Lite, AXI4, AXI5-Lite, TileLink, Avalon, and Wishbone, as well as proprietary buses. Since many of these buses run on different clocks, we also automatically generate any clock-domain-crossing (CDC) logic needed. This ensures that your design has no risk of metastability across asynchronous domains.

We even help you write your low-level software. IDesignSpec GDI and IDS-Batch CLI tools generate C/C++ headers to define your registers and memories. In addition, our IDS-Validate tool generates C/C++ tests to configure and access the registers. We generate a validation environment to run this code on your embedded processors within a UVM testbench. You can also run this code on the “bare metal” design in emulation and even on the actual chip in the bringup lab. Many of our customers use the code we generate as building blocks for their production drivers and embedded programs.

Integrating Third-Party IP

No matter how smart they are, no design team today develops an entire SoC from scratch. They reuse parts of their own previous designs and make extensive use of IP downloaded from shareware sites or licensed from commercial providers. IP suppliers often document their offerings using standards such as IP-XACT and SystemRDL. Our support for these standards makes it much easier for you to use third-party IP without having to tediously copy lots of information. IDesignSpec understands the IP you’re integrating and can handle it along with your own design blocks.

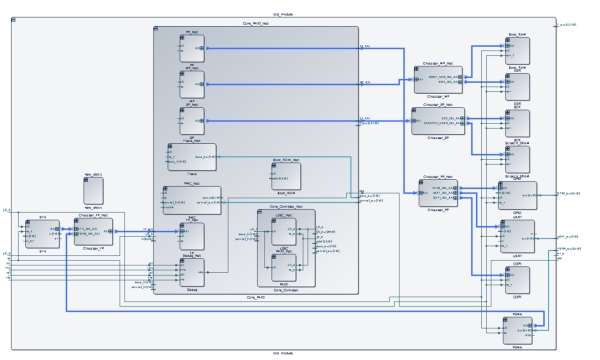

We also help you assemble a chip containing third-party IP. Our IDS-Integrate tool takes your specification for block interconnection and automatically generates the complete top-level RTL design with all the blocks wired together. Manual interconnection is tedious and prone to typos and other errors. Many signal names are very similar, with only a letter or number for differentiation. Typing in tens of thousands of signal names by hand is asking for trouble. Having to manually edit every time your design changes is even worse. Automation with IDS-Integrate addresses these challenges.

Design Packaging and Delivery

This topic is rather broad, so let me touch on two important aspects. One part of packaging is assembling the complete SoC, which I just described. Because we support standard interfaces, IDS-Integrate also generates any bus “widgets” (bridges, converters, aggregators, crossbars, multiplexers, etc.) as needed. Our Silicon IP Portfolio provides many options. Whenever a block or the interconnection specification changes, we re-generate the correct-by-construction design at the push of a button.

The other important aspect is the total package delivered with the design. If you’re developing an IP block for internal or external consumption, or if your chip may be reused someday, you need to provide a lot more than RTL. Recipients expect a UVM testbench and tests, a hardware-software validation environment, C/C++ code for the software side of the HSI, and high-quality documentation. Only IDesignSpec automatically provides all these collateral files along with your RTL design.

A Single Source of Information

At the heart of specification automation lies the concept that an executable specification is the single, golden source of information about a chip or IP design. Generating as many files as possible from that specification ensures that all your project teams are always in sync. Re-generating whenever the specification changes ensure that your teams stay in sync and are always up to date. Our support for standard specification formats means that it’s always easy to add new blocks to your design.

A single source with automated generation is the reason we’re in business. Our solutions save our users weeks or months of effort, eliminate whole classes of errors, and make design iterations painless. Your result is a higher quality design in less time using fewer resources. I invite you to contact us to learn more, see a demo, or request an evaluation license. You’ll be glad you did!