On 13 March 2024, Arm announced its latest and greatest processor cores targeted at automotive applications. These are the Arm Cortex-A720AE, formerly known as HunterAE, and the Arm Cortex-A520AE, formerly known as HayesAE. Both these cores implement the state-of-the-art Armv9 Instruction Set Architecture (ISA).

In addition to one or more Arm processor clusters, each comprised of multiple processor cores and a DynamIQ Shared Unit (DSU), integrating one or more cores with an L3 memory system, today’s system-on-chip (SoC) devices intended for automotive applications typically involve hundreds of other intellectual property (IP) functional blocks. These components include hardware accelerators, graphics processing units, neural processing units, on-chip memory, memory controllers for off-chip memory, and a wide variety of communications and peripheral functions.

Many of these IPs will be sourced from trusted third-party vendors. However, one or more proprietary IPs that differentiate an SoC from its competitors may be developed in-house, as well as the software for differentiation. All these IPs need to be connected to talk to each other at high speed with low latency and low power consumption. Also, this on-chip interconnect must use as few wires as possible to avoid routing congestion. The solution adopted by the vast majority of automotive SoC developers is a network-on-chip (NoC).

In the same way that Arm leads in providing the processor portion of automotive SoCs, Arteris is a leader in this market with respect to network-on-chip interconnects. In fact, per management and analyst estimates, more than 70% of today’s automotive ADAS SoCs shipped have an Arteris NoC inside.

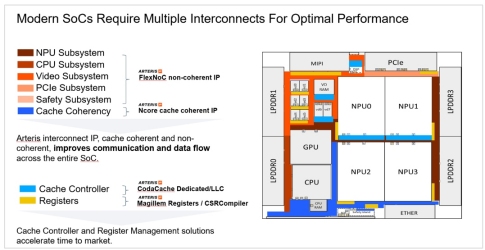

There are two main types of NoCs: coherent and non-coherent. Arm processor clusters contain their own L1, L2 and L3 caches and are internally cache coherent. If the SoC includes only a single processor cluster, and if no other IPs need to maintain fine-grained cache coherency with the processors, then a non-coherent NoC interconnect like Arteris FlexNoC may be employed. However, if the SoC contains multiple processor clusters, which is increasingly popular, and some other IPs need to maintain cache coherency, then a coherent NoC interconnect like Arteris Ncore will be required. A prevalent scenario is for both coherent and non-coherent NoCs to be employed in the same SoC as shown in Figure 1.

Figure 1: Modern SoCs require cache coherent and non-coherent interconnects from Arteris

So, why does Arteris enjoy such a commanding lead concerning including its NoC interconnects in automotive SoCs and other industries? Wouldn’t it be better for the SoC team to adopt a roll-your-own approach simply? The short answer is no, which explains why most automotive ADAS SoC teams opt to use NoC interconnect technology from Arteris. The longer answer can be summed up below.

Productivity

An SoC team might argue that if they create an interconnect in-house, then they will be able to customize and fine-tune it to their specific requirements. However, there are several potential problems with this approach. For example, interconnects, in general, and coherent interconnects, in particular, are complex beasts; creating one from scratch demands a high level of expertise. Then there’s the fact that requirements tend to evolve over time, especially if the plan is to reuse this interconnect for other SoCs in the future.

A NoC interconnect is essentially an IP that spans the entire SoC. Creating a NoC interconnect will require its dedicated team. Even worse, it’s hard to tell if you are debugging the chip or debugging the NoC regarding chip integration.

Users who have built their own coherent interconnect in-house typically report that it can sometimes take over 50 person-years to develop and debug. And that’s only the beginning because this is when the maintenance part commences. This may explain why these teams subsequently employ Arteris NoC interconnects in future projects, enabling them to achieve operational readiness with their NoC implementations from the very first day.

A key contributor to the effort here is that the various blocks to be integrated can use many different protocols and protocol versions at their interfaces, and all of them need to be made sense of and translated. Arteris provides reusable and configurable library components that developers can reuse, including directory management for directories tracking cache coherency.

Configurability and Scalability

Some interconnects are tailored to implement large mesh topologies featuring arrays of homogeneous processing elements. This may be advantageous for SoCs intended for deployment in data centers, but it doesn’t favor SoCs destined for use in automotive applications. This is because automotive SoCs typically feature a heterogeneous mix of processing elements, along with IPs sourced from multiple vendors, all featuring different data widths, clock frequencies, and protocols.

Happily, Arteris NoC interconnects IP can support any topology, including crossbar, star, tree, and mesh. They can even enable multiple NoC topologies in the same device and generate configurations automatically based on user specifications. As indicated above, Arteris NoC IP has a suite of sockets or interface elements. In addition to supporting configurable data widths and clock frequencies, these sockets also support the various protocols adopted by the SoC industry.

Safety

Functional Safety (FuSa), per ISO 26262, is the absence of unacceptable risk due to hazards caused by faulty operation of electrical and electronic systems. For a component, subsystem, or system to be legitimately considered functionally safe, it should undergo independent certification according to the ISO 26262 standard. Once a product is certified, it may be rightfully claimed as functionally safe, aligning with a specific Safety Integrity Level (SIL).

The ISO 26262 standard outlines a risk classification scheme known as Automotive Safety Integrity Level (ASIL), which is specifically designed to assess the functional safety of road vehicles. Arteris NoC IP is ASIL D and ASIL B certified for Hardware Safety Integrity. Furthermore, Arteris' SoC Integration Automation tools have achieved comprehensive TCL1 compliance in accordance with the ISO 26262 standard, as verified through an independent assessment conducted by TÜV SÜD.

Risk Mitigation

Many companies can make impressive claims about their capabilities, but when building an SoC, it’s crucial to ensure that a critical element like the NoC is not the weak link in the chain. In terms of coherency, for example, it’s essential to determine if your existing NoC supports ACE or CHI-B. Unfortunately, it may not be compatible if you use Arm’s latest automotive processors, notably the aforementioned Arm Cortex-A720AE and Arm Cortex-A520AE processors and their associated DSU, because these offer coherency support in CHI-E.

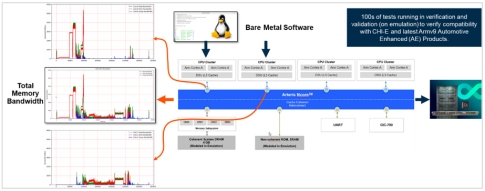

Arm and Arteris are long-time partners. Extensive emulation evaluations on a test-bench system based on these processors and other IPs have already been performed using early access to Arm's processors. The testing extended to booting Linux and using it with associated drivers to perform various system-level tasks, as indicated in Figure 2.

Figure 2: Emulation Validation Environment

Conclusion

If you are planning on developing an automotive SoC using Arm’s latest and greatest automotive processors, engaging with the NoC experts at Arteris not only provides access to our comprehensive offerings but also helps to avoid common pitfalls. If nothing else, this collaboration will provide insights to enable you to make an informed decision as to the best way to implement your interconnect.

Frank Schirrmeister, VP solutions and business development at Arteris, leads activities in the automotive, data center, 5G/6G communications, mobile, aerospace and data center industry verticals. Before Arteris, Frank held various senior leadership positions at Cadence Design Systems, Synopsys and Imperas, focusing on product marketing and management, solutions, strategic ecosystem partner initiatives and customer engagement.