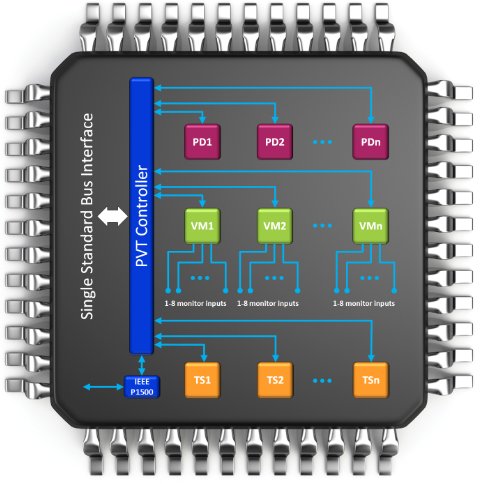

Jan. 07, 2016, Jan. 07, 2016 – Moortec Semiconductor Limited, provider of embedded die monitoring IP solutions for advanced nodes, announces its new PVT Controller. The PVT Controller provides a single standard interface to Moortec's embedded Process, Voltage and Temperature (PVT) sensing Sub-System used to increase System on Chip performance and reliability.

On-chip PVT monitoring is now a key consideration for 28-nanometer (nm) and FinFET technology based designs. Higher accuracy monitors embedded within SoC designs enable a greater opportunity for dynamic performance optimisation, either for lower power or higher data throughput as well as offering greater device reliability. Sensing die temperature, detecting logic speed and monitoring voltage supply levels can be used intelligently to vary system clock frequencies and the voltage levels of supply domains. A benefit of embedded thermal monitoring in particular is to enhance device reliability and life-time by assessing the electromigration effects of hot spots within the chip.

A key aspect is that PVT data collection can be applied to each and every device, either during production or 'in-the-field'. Moortec believe that strategies adopted by IC designers over the coming years will be heavily influenced by the analysis of data harvested from in-chip monitors.

"The greater process variability that is apparent at these challenging small geometry CMOS technologies is forcing the IC design community to look at conditions on-chip, not just generally but also per device and within regions of a device," said Stephen Crosher, Managing Director of Moortec Semiconductor. "The industry faces the challenge posed by demand for increasingly integrated, increasingly functional, giga-scale ICs for applications such as personal mobile technology and multi-core server configurations, whilst trying to improve battery life and maintaining optimal performance. At low-geometry nodes, interconnect resistances are dramatically increasing, core supply headroom is reducing and the power consumption per unit area of silicon is increasing. Our flexible and easy-to-integrate PVT Controller Sub-System is well placed to enable Dynamic Voltage and Frequency Scaling (DVFS) optimisation schemes to be used within the designs."

By incorporating the PVT Controller, the design of the customer's host system is greatly simplified providing many features for the access and control of on-chip PVT monitors. Moortec are currently developing their roadmap of innovative next generation in-chip monitoring products.

About Moortec Semiconductor

Moortec Semiconductor, established in 2005, provide high quality analog and mixed-signal Intellectual Property (IP) solutions world-wide specialising in die monitoring solutions. Having a track record of delivery to tier-1 semiconductor and product companies, Moortec provide a quick and efficient path to market for customer products and innovations. For more information please visit www.moortec.com.