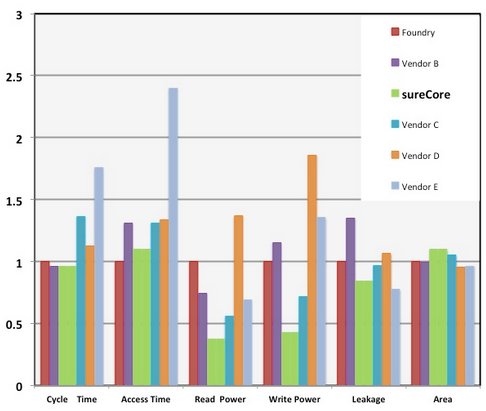

Dynamic power savings exceeding 50% and reduces static power by up to 35%

Sheffield, England, Jan. 19, 2016 – sureCore Ltd., the low power SRAM IP leader, today announced the immediate availability of its 28nm Fully-Depleted Silicon-on-Insulator (FDSOI) memory compiler.

The compiler supports the company's low power, Single Port SRAM IP and Dual Port SRAM IP for 28nm FDSOI process technology. It offers capacities up to 1Mbit with word lengths up to 288bits and supports 4, 8 and 16 Mux factors.

The sureCore Single Port SRAM IP supports a wide operating voltage range of 0.6-1.2V and boasts dynamic power savings exceeding 50% of current commercial offerings. The IP also cuts static power by up to 35% with only a modest <10% area penalty.

The sureCore compiler allows designers to make trade-offs between various SRAM sizes in terms of number of words, word length and multiplex factor. It automatically generates datasheets, simulation (Verilog), layout (LEF) and timing/power (Liberty) models to enhance and speed the design process.

"The availability of this new compiler marks a key milestone for sureCore and demonstrates that the power saving technologies we developed are now available to the SoC design community," said sureCore's Chairman, Guillaume d'Eyssautier. "This marks the start of a new era for low power electronics."

sureCore's silicon-proven, 28nm FDSOI IP targets IoT and other applications that demand long battery life with minimal operating and stand-by power performance. The IP also provides considerable value in the networking space where power and heat dissipation are critical.

sureCore will follow the 28nm FDSOI compiler with a 40nm Ultra-Low power compiler in March of 2016 that targets the leading foundry process. The company's product roadmap also includes the introduction of a 40nm CMOS Ultra Low Power SRAM later next year. Work also continues on a 28nm CMOS solution.

"There is still considerable innovation happening at relatively mature production nodes," said sureCore's CEO, Paul Wells. "With the growing IoT market, mature nodes such as 40nm are 28nm are taking on an extended life. Their cost performance is ideal for the IoT technical and business challenges."

Power Comparison Chart

About sureCore

sureCore Limited is an SRAM IP company based in Sheffield, UK, developing low power memories for current and next generation, silicon process technologies. Its award-winning, world-leading, low power SRAM design is process independent and variability tolerant, making it suitable for a wide range of technology nodes. This IP will help SoC developers meet both challenging power budgets and manufacturability constraints posed by leading edge process nodes.