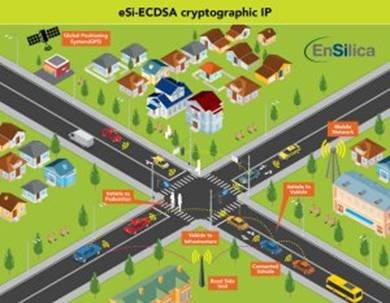

Wokingham, UK, May. 09, 2016 – EnSilica, a leading independent provider of semiconductor solutions and IP, has launched the eSi-ECDSA cryptographic IP designed to help meet the high security communication and latency requirements of automotive Car2Car and Car2Infrastructure (Car2x) applications that form part of today's emerging Intelligent Transport Systems.

EnSilica's eSi-ECDSA cryptographic IP is fully compliant with the IEEE 1609.2 and ETSI TS 103 97 standards. These standards define the security layers in the Car2x communication protocols where cryptographic algorithms are the primary tools used to safeguard against information security risks such as message confidentiality, integrity, availability and authenticity. In particular, the Elliptic Curve Digital Signature Algorithm (ECDSA) is specified for message authentication, the Elliptic Curve Integrated Encryption Scheme (ECIES) for asymmetric encryption and the Advanced Encryption Standard (AES) for symmetric encryption.

EnSilica's eSi-ECDSA is an ASIC acceleration core that has been specifically designed to deliver the high level of message-signature verifications required by Car2x ECDSA message authentication, where practical requirements range between 400 to 4000 verifications per second depending on the message beaconing rate (1Hz to 10Hz) and expected worst case vehicle densities on the road. This overcomes the slow verification rates of traditional embedded software cryptographic algorithm implementations which typically only deliver message-signature verifications in the order of 10's per second. eSi-ECDSA achieves this by off-loading the ECDSA signing and verification operations so that the processor is only required to load and read back results via an APB or AHB interface.

In addition, the eSi-ECDSA core features a range of lower level ECC operations which allow the acceleration of ECIES asymmetric encryption, flexible real-time key selection, support for all commonly standardized curves (such as NIST, SEC2 and Brainpool), and resistance against timing/power analysis attacks.

"With safety dependent on the underlying communication security of today's emerging Car2x applications, the performance demands being placed on the prescribed cryptographic algorithms far outweigh the capabilities of traditional embedded software implementations," said Ian Lankshear, CEO of EnSilica. "As an ASIC acceleration core that off-loads the arithmetic intensive tasks from the main processor, our eSi-ECDSA cryptographic IP has been designed to easily meet the practical performance requirements demanded by Car2x message authentication."

About EnSilica

EnSilica was founded in 2001 and has a strong track record of success in delivering ASIC and FPGA based solutions to semiconductor companies and OEMs worldwide. The company is headquartered in the UK and has subsidiaries in India and the USA. The company is a specialist in low-power ASIC design and complex FPGA-based embedded systems. In addition to supplying IP and turnkey ASIC/FPGA development and supply, EnSilica also provides point services to companies with in-house ASIC design teams. These services include system engineering, analog and mixed signal design, and advanced verification using UVM, DFT and physical implementation. For further information about EnSilica, visit http://www.ensilica.com.