Meylan, France, June 4, 2018 -- Dolphin Integration announces the availability in free download of its innovative IDE SmartVisionTM supporting the RISC-V Instruction Set Architecture (ISA).

A suitable software development environment is fundamental for optimizing designs in terms of power consumption, area (code density) and performances. Thanks to its IDE, Dolphin integration enables early in the design flow to meet these requirements.

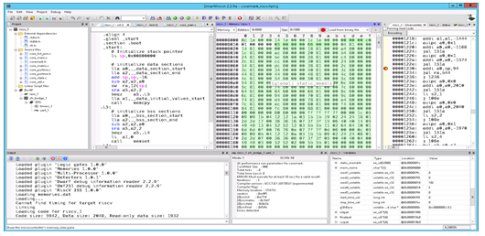

SmartVisionTM is an open environment allowing the design of complete subsystems based on processor cores and peripherals. It provides an intuitive interface as well as the necessary tools to debug embedded software by simulation or by In Circuit Emulation. Its key benefits include:

The support of RISC-V through the RV32 Tornado subsystem offers a complete turnkey solution to configure and optimize ultra-low power SoCs. It includes:

Furthermore, for easy compatibility with the RISC-V ecosystem, the support of the upcoming debug specification is in progress.

The SmartVisionTMIDE is in free download. For more information, please contact us at contact@dolphin.fr

About Dolphin Integration

Dolphin Integration is a pioneer in Energy-Efficient Systems-on-Chip enablement. The company serves a growing range of applications from battery-operated to line-powered. Its portfolio of more than 200 silicon IPs covering Foundation, Feature and power Fabric IPs are proven and available in multiple processes and foundries. This coherent portfolio allows to reduce SoC power consumption in sleep, triggering and active processing modes. The company is committed to its customer success through constant innovation, quality control and dedicated support. Dolphin Integration comes with 30 years experience in integration of silicon IP components leveraging power-integrity driven simulation tools to design and supply cost-effective logic and mixed-signal ASIC/SoC.