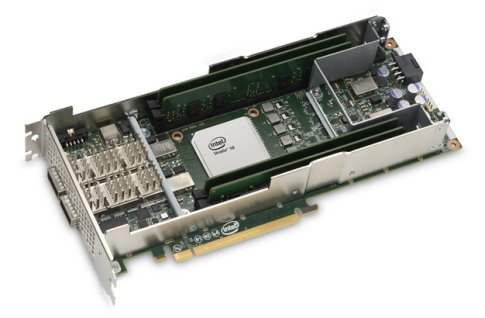

September 25, 2018 -- Intel today extended its field programmable gate array (FPGA) acceleration platform portfolio with the addition of the new Intel® Programmable Acceleration Card (PAC) with Intel® Stratix® 10 SX FPGA, Intel’s most powerful FPGA. This high-bandwidth card leverages the Acceleration Stack for Intel® Xeon® CPU with FPGAs, providing data center developers a robust platform to deploy FPGA-based accelerated workloads. Hewlett Packard Enterprise* will be the first OEM to incorporate the Intel PAC with Stratix 10 SX FPGA along with the Intel Acceleration Stack for Intel Xeon Scalable processor with FPGAs into its server offering.

“We’re seeing a growing market for FPGA-based accelerators, and with Intel’s new FPGA solution, more developers – no matter their expertise – can adopt the tool and benefit from workload acceleration. We plan to use the Intel Stratix 10 PAC and acceleration stack in our offerings to enable customers to easily manage complex, emerging workloads.”

–Bill Mannel, vice president and general manager, HPC and AI Group, HPE

What It Does: Like the previously announced Intel PAC with Intel® Arria® 10 FPGA, this new Intel PAC with Stratix 10 SX FPGA supports an ecosystem of design partners that delivers IP to accelerate a wide range of application workloads. The Intel PAC with Stratix 10 SX FPGA is a larger form factor card built for inline processing and memory-intensive workloads, like streaming analytics and video transcoding. While the smaller form factor Intel PAC with Arria 10 FPGA is ideal for backtesting, data base acceleration and image processing workloads.

Why It’s Important: As the demands for big data and artificial intelligence (AI) increase, the reprogrammable technology of the FPGA meets the processing requirements and changing workloads of data center applications. With reconfigurable logic, memory and digital signal processing blocks, FPGAs can be programmed to execute any type of function with high throughput and real-time performance, making them ideal for many critical enterprise and cloud applications.

The acceleration stack for Intel Xeon CPU with Intel FPGAs works with industry-leading OS, virtualization and orchestration software partners, providing a common interface for software developers to get faster time to revenue, simplified management and access to a growing ecosystem of acceleration workloads.

What the Solution Includes:

More Context: Programmable Solutions Group News

The Small Print: Intel technologies’ features and benefits depend on system configuration and may require enabled hardware, software or service activation. Performance varies depending on system configuration. No computer system can be absolutely secure. Check with your system manufacturer or retailer or learn more at intel.com.