Nov. 06, 2025 –

Sydney, Australia — Perceptia Devices, a leader in high-performance clocking IP, today announced the availability of an updated design kit for its pPLL03 phase-locked loop IP on GlobalFoundries’ 22FDX® (22nm FD-SOI) technology node.

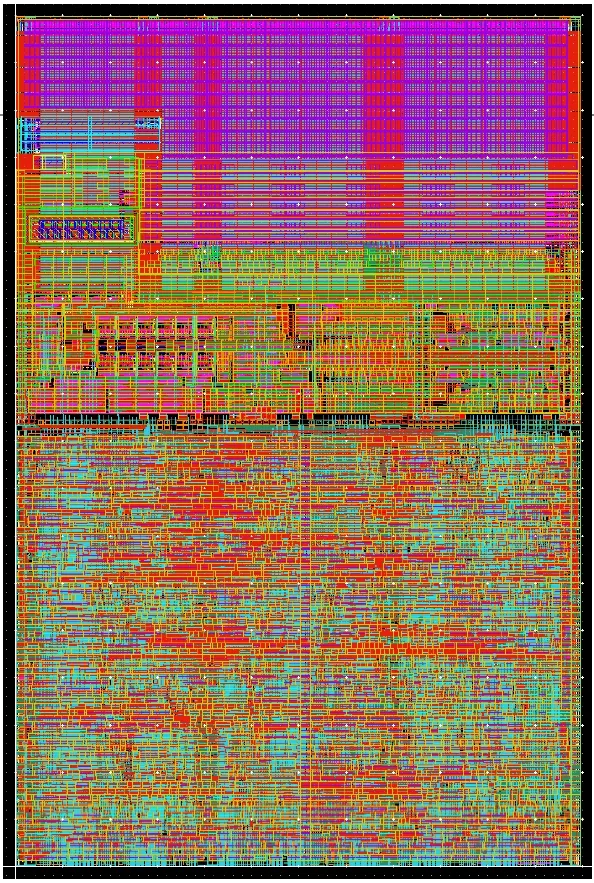

The pPLL03 is Perceptia’s low jitter, high-performance PLL IP core targeted at demanding SoC applications including AI accelerators, microprocessors, ADC/DAC sampling clocks, and high-speed digital subsystems. The release of the design kit enables SoC developers to efficiently incorporate the pPLL03 into their designs with full support for layout, simulation, and timing closure.

This update upgrades pPLL03 to include a power conditioning circuit that makes it more tolerant to power supply noise and allows pPLL03 to be more reliable in a range of environments.

Key technical features of the pPLL03 include:

The pPLL03 supports both integer-N and fractional-N synthesis, allowing for fine-grained frequency generation. Its all-digital control interface enables easy integration with standard digital flows and software-driven configuration.

“Our goal with pPLL03 was to deliver best-in-class jitter performance with integration flexibility in advanced nodes like GlobalFoundries 22FDX,” said Julian Jenkins, CTO at Perceptia. “The silicon data validates our design and methodology, and the IP is production-ready.”

GlobalFoundries’s 22FDX platform is tailored for low-power, high-density applications such as mobile, edge AI, RF connectivity, and embedded processing. The availability of pPLL03 in this process gives customers a differentiated clocking solution optimised for FD-SOI characteristics.

The pPLL03 design kit includes:

The kit is available immediately to qualified licensees.

For licensing inquiries or to request a technical brief, contact sales@perceptia.com or visit www.perceptia.com.

PLL03 is a compact, low-jitter phase-locked loop (PLL) IP core optimised for advanced process nodes. Delivering output clock frequencies up to 4GHz, pPLL03 is designed for use in a wide range of high-performance applications including high-performance computing, AI acceleration and timing-critical logic, it delivers superior jitter and integration flexibility. pPLL03 is especially suited for designs with many clock domains. pPLL03 enables designers to confidently implement advanced timing architectures without compromising on area or power.

Perceptia Devices is an IP and design services provider, based in Sydney, Australia. With a focus on PLLs and precision timing, Perceptia supports customers across a wide range of applications including wireless communications, AI/ML, data converters, IoT, and mixed-signal SoCs with high performance, low area PLLs.

For more information or to request the pPLL05 datasheet, please contact:

ð"§sales@perceptia.com

ðwww.perceptia.com