January 24, 2018 -- Device Level Ring (DLR) is a Layer-2 protocol that provides media redundancy in a ring topology. The DLR protocol is intended primarily for implementation in Ethernet/IP end-devices that have two Ethernet ports and embedded switch technology. The DLR protocol provides fast network fault detection and reconfiguration in order to support the most demanding control applications.

A DLR network includes at least one node configured to be a Ring Supervisor, and any number of Beacon Based Nodes. It is assumed that all the ring nodes have at least two Ethernet ports and incorporate embedded switch technology.

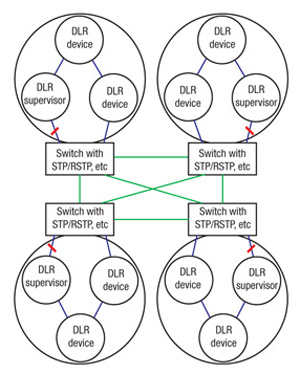

The new realease of SoC-e’s MES IP Core (Managed Ethernet Switch) fully supports DLR protocol. The IP Core allows to implement a DLR end-device, with embedded switching capabilities and supports multiple Ethernet interfaces. The following network node configurations can be implemented with the MES IP Core: