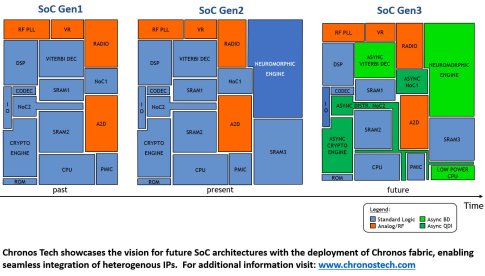

SAN DIEGO -- September 25, 2018 -- The trend of adding features to a System on Chip (SoC) is growing exponentially. Market demand is causing significantly diverse Intellectual Properties (IPs) to interact with each other, but the integration of such IPs with traditional architectures is proving to be a major challenge. Chronos Tech has developed groundbreaking solutions for addressing complex IP integration and achieving aggressive Performance, Power and Area (PPA) optimizations.

With the proliferation of Artificial Intelligence (AI) and Machine Learning (ML), modern SoCs today are monolithic chips that have neuromorphic engines as stand-alone IPs to help speed up real time decisions and accelerate computer vision and/or speech recognition. Such IPs, which are asynchronous in nature, have been deployed in silicon as their synchronous counterparts (often utilizing GPU cores acting as neural networks) but the real advantage in terms of performance over power will be achieved with the integration of asynchronous neuromorphic engines, mimicking the biological behavior of the brain. “The vision for the future is even more intricate, where it will be imperative to be able to choose different IPs and fabrics and seamlessly integrate them to meet everchanging customer demands” says Stefano Giaconi, Chronos Tech’s Chief Technology Officer.

Chronos Tech’s patented Fabric is specifically designed for this purpose. It not only enables connection between synchronous IPs with reduced routing and optimized latency, but it can easily integrate any flow-control or credit-based protocols to any asynchronous channel, providing also a conversion of different channel styles if needed. It can also be used to connect two different asynchronous IPs with reduced routing, making it the ideal candidate for heterogeneous IP integration. “We are the only fabric today which overcomes these challenges without the cost of extra area and latency” claims Giacomo Rinaldi, Chronos Tech’s VP of Engineering.

Chronos Tech is currently working with leading semiconductor companies to evaluate the deployment of the Chronos Tech Fabric.

About Chronos Tech

San Diego-based Chronos Tech is a leader in IPs and architectural solutions that enable the development of next-generation complex SoCs. They leverage existing validated design flows with cutting-edge circuit innovations that can be optimized for routing, latency, and power. For more information, visit www.chronostech.com.