Mar. 13, 2024, Mar. 13, 2024 –

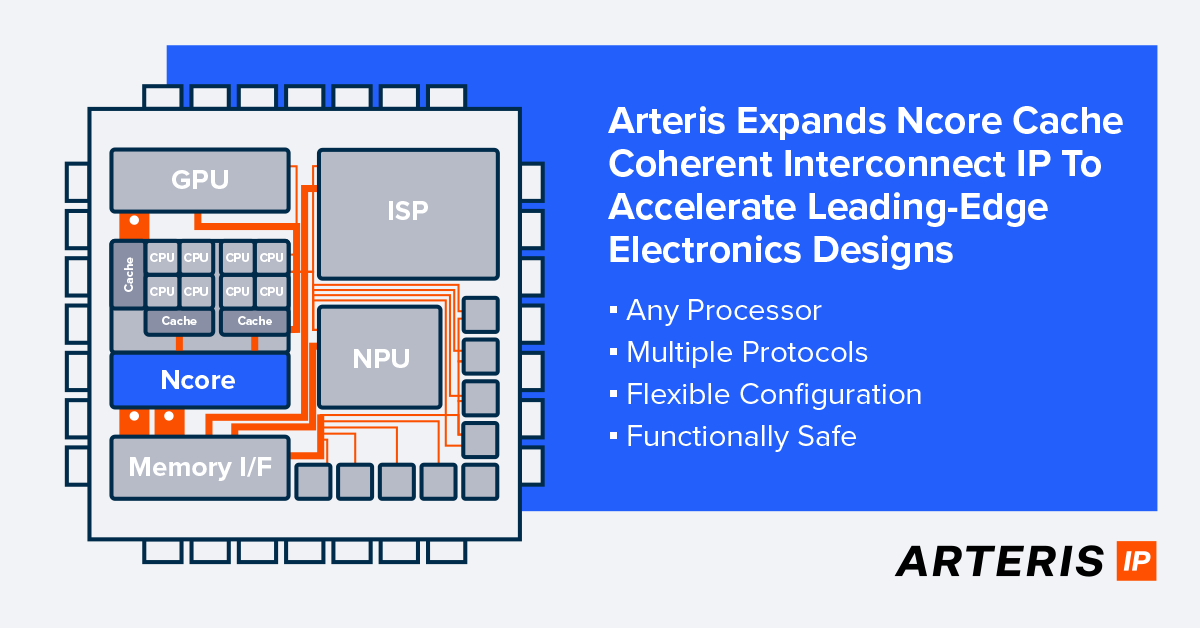

Arteris, Inc. (Nasdaq: AIP), a leading provider of system IP which accelerates system-on-chip (SoC) creation, today announced the immediate availability of the latest release of Ncore cache coherent network-on-chip (NoC) IP. Ncore ensures low latency integration of hardware accelerators into a coherent domain, enabling the speed and efficiency required for cutting-edge applications in complex SoC designs. Deploying Ncore can save SoC design teams upwards of 50 years of engineering effort per project compared to manually generated interconnect solutions.

The latest release of Ncore works with multiple processor IPs, including RISC-V and the next-generation Armv9 Cortex processor IP. Ncore boasts multi-protocol support, allowing seamless integration of IPs connected to the same NoC fabric. Designers can choose from CHI-E, CHI-B and ACE fully coherent agent interfaces and ACE-Lite IO-coherent interfaces. AXI is also supported for interfacing with sub-systems or devices without coherency requirements. These capabilities enhance the flexibility and adaptability of Ncore, making it an ideal solution for complex and evolving SoC designs, including safety-critical applications.

"We have worked with Arteris network-on-chip technology since 2010, using it in our advanced autonomous driving and driver-assistance technologies,” said Leonid Smolyansky, Ph.D.

SVP SoC Architecture, Security & Safety at Mobileye. “We are excited that Arteris has brought its significant engineering prowess to help solve the problems of fault tolerance and reliable SoC design.”

With configurability and scalability at its core, Ncore empowers SoC designers to meet specific power, performance and area requirements with the flexible fine-tuning of the NoC architecture. Ncore is also ISO 26262 certified, helping design teams address the critical demands of automotive and industrial safety applications with requirements from ASIL B to ASIL D. Ncore’s ISO 26262 certification underscores Arteris' ongoing commitment to delivering safe, secure and reliable technology to its global customers.

“SoC designers are challenged by the growing complexity resulting from the number of processing elements, multiple protocols and functional safety requirements of modern electronics,” said K. Charles Janac, president and CEO of Arteris. “Our latest release of a production-proven Ncore marks an important milestone towards our ultimate cache coherent interconnect IP vision to connect any processor, using any protocol and topology.”

Ncore supports direct connections for heterogeneous, asymmetric systems and other flexible connectivity options, ensuring adaptability to various applications across automotive, industrial, communications and enterprise computing markets. Ncore cache coherent interconnect IP is an ideal companion to FlexNoC, Arteris’ industry-leading non-coherent interconnect IP. For more information about Ncore from Arteris, please visit https://www.arteris.com/products/coherent-noc-ip/ncore/.

About Arteris

Arteris is a leading provider of system IP for accelerating system-on-chip (SoC) development across today’s electronic systems. Arteris network-on-chip (NoC) interconnect IP and SoC integration automation technology enable higher product performance with lower power consumption and faster time to market, delivering better SoC economics so its customers can focus on dreaming up what comes next. Learn more at arteris.com.