Stream Buffer Controller

The IP core is highly configurable in terms of operation mode, buffer size and buffer address for each stream. The configuration is done over a memory mapped slave interface, either by an embedded-CPU, by a FPGA Manager application or by an application specific stream configurator controller in VHDL.

View Stream Buffer Controller full description to...

- see the entire Stream Buffer Controller datasheet

- get in contact with Stream Buffer Controller Supplier

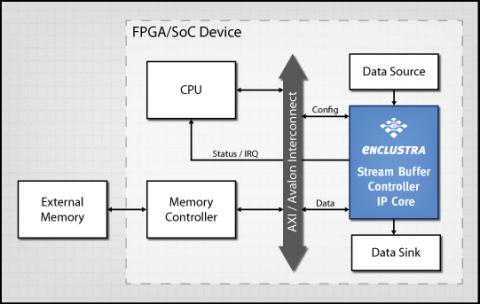

Block Diagram of the Stream Buffer Controller IP Core

Stream Buffer Controller IP

- Stream Buffer Controller

- PCIe 5.0 Controller supporting Endpoint, Root Port, Switch, Bridge and advanced features

- PCIe 5.0 Controller with AMBA AXI interface

- Compute Express Link (CXL) 2.0 Controller with AMBA AXI interface

- PCIe 2.1 Controller supporting Root Port, Endpoint, Dual-mode Configurations, with Built-in DMA and Configurable AMBA AXI Interconnect

- PCIe 1.1 Controller supporting Root Port, Endpoint, Dual-mode Configurations, with Built-in DMA and Configurable AMBA AXI Interconnect