32-Bit RISC-V Embedded Processor and Subsystem. Maps ARM M-0 to M-4. Optimal PPA.

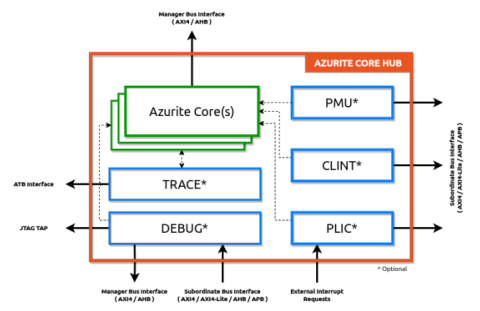

The Azurite core comes bundled as a compute subsystem, with integrated AMBA protocol interconnects (supports AXI4, AHB, APB) and uncore components (debug, trace, interrupt controllers etc).

View 32-Bit RISC-V Embedded Processor and Subsystem. Maps ARM M-0 to M-4. Optimal PPA. full description to...

- see the entire 32-Bit RISC-V Embedded Processor and Subsystem. Maps ARM M-0 to M-4. Optimal PPA. datasheet

- get in contact with 32-Bit RISC-V Embedded Processor and Subsystem. Maps ARM M-0 to M-4. Optimal PPA. Supplier

Block Diagram of the 32-Bit RISC-V Embedded Processor and Subsystem. Maps ARM M-0 to M-4. Optimal PPA.

32-Bit IP

- RISC-V ARC-V RMX-100 Ultra-low Power 32-bit Processor IP for Embedded Applications

- ARC-V RMX-500 power efficient 32-bit RISC-V processor for embedded applications

- ARC-V RHX-105 dual-issue, 32-bit RISC-V processor for real-time applications (multi-core)

- ARC-V RMX-100 ultra-low power 32-bit RISC-V processor for embedded applications

- ARC-V RHX-100 dual-issue, 32-bit single-core RISC-V processor for real-time applications

- Compact, low-power 32-bit RISC CPU