MIPI CSI-2 v3.0 Rx/Tx For Combo C/D-PHY

Features

- Compliant with MIPI CSI Standard v3.x, v2.x , v1.x and MIPI D-PHY Standard v1.x, MIPI D-PHY Standard V2.x and MIPI C-PHY V1.x

- Up to 3 Gsps per trio using C-PHY. 17Gbps in 3 Trios.

- Up to 2.5 Gbps per data lane of D-PHY (V2.0). 10Gbps in 4 Lanes

- Programmable 1, 2, 3 (C-PHY) or 4 (D-PHY) Data Lane Configuration.

- Configurable up to 4 Virtual Channels

- Operate in continuous and non-continuous clock modes.

- Color Modes: 16, 18, 24 and 36 bpp

- Color Formats: YUV420 8, 10bits and without CSPS and Legacy, YUV422 8, 10bits, RGB-888, 565, 666, 555 and 444. RAW6, 7, 8, 10, 12 and 14.

- Register configuration through CCI interface

- Host Interface can be Pixel or AXI interface.

View MIPI CSI-2 v3.0 Rx/Tx For Combo C/D-PHY full description to...

- see the entire MIPI CSI-2 v3.0 Rx/Tx For Combo C/D-PHY datasheet

- get in contact with MIPI CSI-2 v3.0 Rx/Tx For Combo C/D-PHY Supplier

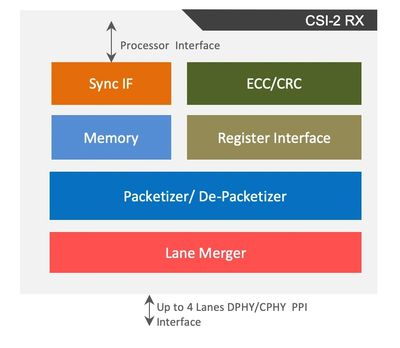

Block Diagram of the MIPI CSI-2 v3.0 Rx/Tx For Combo C/D-PHY

Csi IP

- MIPI CSI DSI C-PHY IP for TSMC (5nm, 6/7nm, 12/16nm, 22nm, 28nm, 40nm)

- MIPI CSI DSI Controller - CPHY CSI-2 Transmitter v 2.1, Compatible with MIPI C-PHY v1.2 & DPHY v2.1.

- MIPI D-PHY Universal Tx / Rx v1.1 @1.5ghz Ultra Low Power for IoT & Wearables

- MIPI D-PHY Receiver for CSI-2 of TSMC 40nm LP

- Camera sub-LVDS/mini-LVDS/LVDS/HiSPi(SLVS-400, HiVCM)/MIPI-DPHY/CMOS 6-7mode Combo-Receiver 1.5Gbps

- CSI2 TX; Camera Serial Interface, MIPI Compliant