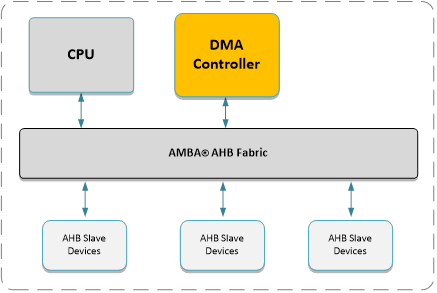

AHB Single Channel DMA Controller

Once set up, the DMA controller is primarily an AHB Master, which initiates data transfers across the AHB bus to/from a peripheral device through the DMA Buffer. The DMA Buffer is a scalable x32bit FIFO, which is useful for peripheral devices requiring a steady stream of data such as an LCD Controller, Ethernet MAC or other communication device.

The DMA controller contains useful features such incrementing and non-incrementing addressing and link list operation. Linked list support is useful for non-contiguous memory transfer operations.

Multiple DMA controllers can be placed in the AHB System to provide multiple channel DMA control.

View AHB Single Channel DMA Controller full description to...

- see the entire AHB Single Channel DMA Controller datasheet

- get in contact with AHB Single Channel DMA Controller Supplier

Block Diagram of the AHB Single Channel DMA Controller IP Core

DMA IP

- AXI DMA Back-End Core

- PCIe 5.0 Controller with AMBA AXI interface

- PCIe 2.1 Controller supporting Root Port, Endpoint, Dual-mode Configurations, with Built-in DMA and Configurable AMBA AXI Interconnect

- PCIe 1.1 Controller supporting Root Port, Endpoint, Dual-mode Configurations, with Built-in DMA and Configurable AMBA AXI Interconnect

- AXI4 Memory-Mapped to/from AXI4-Stream DMA

- DMA Back-End Core