Multi Protocol Endpoint IP Core for Safe and Secure Ethernet Network

Compact RISC-V Processor - 32 bit, 3-stage pipeline, 32 registers

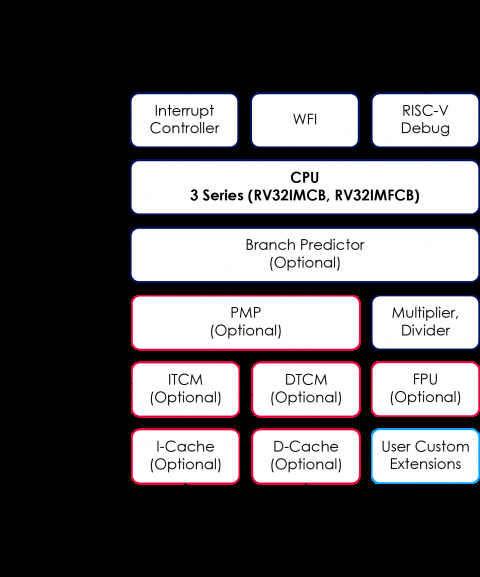

The core includes optional L1 data and instruction caches, optional instruction and data TCM, optional 8 or 16 PMP regions, an interrupt controller and RISC-V Debug module optionally with PC trace.

Like with all Codasip RISC-V cores, it is possible to create custom instructions using Codasip Studio to extend the L30 and to generate corresponding hardware and software development kits.

View Compact RISC-V Processor - 32 bit, 3-stage pipeline, 32 registers full description to...

- see the entire Compact RISC-V Processor - 32 bit, 3-stage pipeline, 32 registers datasheet

- get in contact with Compact RISC-V Processor - 32 bit, 3-stage pipeline, 32 registers Supplier

Block Diagram of the Compact RISC-V Processor - 32 bit, 3-stage pipeline, 32 registers

Processor IP

- RISC-V ARC-V RMX-100 Ultra-low Power 32-bit Processor IP for Embedded Applications

- ARC-V RMX-500 power efficient 32-bit RISC-V processor for embedded applications

- ARC-V RHX-105 dual-issue, 32-bit RISC-V processor for real-time applications (multi-core)

- Secure-IC Securyzr(TM) Cyber Escort Unit IP provides real time detection of sero day attacks on processor

- 64-bit RISC-V Application Processor Core

- 64-bit RISC-V Application Processor Core