Energy Efficient AI & DSP processor in edge computing devices

It has been designed to achieve the lowest power consumption, either with Cores only having 4 pipeline stages and which can be individually clock gated when unused or using Shared Data Memory accessed through a low latency interconnect rather than Data Caches.

Thanks to its different configurability parameters, it can be tailored to exactly match final application use case.

View Energy Efficient AI & DSP processor in edge computing devices full description to...

- see the entire Energy Efficient AI & DSP processor in edge computing devices datasheet

- get in contact with Energy Efficient AI & DSP processor in edge computing devices Supplier

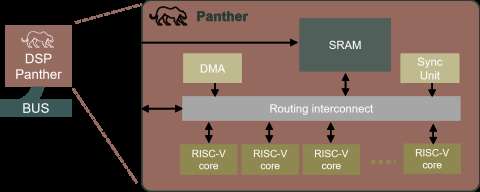

Block Diagram of the Energy Efficient AI & DSP processor in edge computing devices

DSP Processor IP

- Powerful vector DSP for 5G-Advanced Massive Compute

- DSP Extention Processor

- DSP Extention Superscalar Processor

- 32-bit 8-stage superscalar processor that supports RISC-V specification, including GCNP (DSP)

- FFT Processor for Microsemi FPGA

- Highest code density, Low Power 32-bit Processor with optional DSP