Display Driver with on-chip Full-HD frame buffer and a scalable image compression Codec

By Star Sung (TITC-USA), Jacques Baudier (TITC-USA)

Abstract

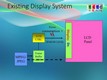

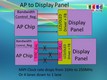

A display Driver with on-chip frame buffer and a scalable image compression codec reaching visually lossless image quality is presented. The frame buffer compression codec can encode and decode up to eight pixels in one clock cycle. Integrating a whole frame buffer with RGB=888 or 10-10-10 bits into the display driver sharply reduces power dissipated between the AP chip and Display board. The existing working chips are manufactured by both UMC and TSMC 55nm high voltage CMOS process. A new chip design with on-chip frame buffer SRAM includes a scalable compression ratio codec supporting HD720 (1280x720), Full-HD (1920x1080), (Max. 2560x1280) is completed which reduces the frame buffer SRAM density and area by a factor ranging from 2.0 times to 6.0 times and cuts the power consumption of the on-chip SRAM frame buffer by ~6.0 times of which 6 times is contributed by less capacitive bit line load. The 2X compression codec having 40K gates in encoder and 15K in decoder accepts both YUV and RGB color formats. A smart engine detects the Tx/Rx bandwidth availability and decides the compression ratio to avoid data congestion. The high image quality is achieved by applying patented proprietary compression algorithms including accurate prediction in DPCM, a new VLC coding with accurate predictive divider and an intelligent bit rate distribution control and an intelligent random truncation mechanism is realized to avoid artifact caused from error propagation.