- Verification IP Catalog >

- Memory >

- DRAM >

- DDR

Simulation VIP for HBM

This Cadence® Verification IP (VIP) provides support for the JEDEC® High-Bandwidth Memory (HBM) DRAM device standard. It provides a mature, highly capable compliance verification solution that supports simulation, formal analysis, and hardware acceleration platforms, making it applicable to intellectual property (IP), system-on-chip (SoC), and system-level verification. The Memory Model for HBM models a single channel of HBM DRAM; this model can be replicated for multiple channels and multiple ranks. The Memory Model for HBM runs on all leading simulators, and leverages the industry-standard Cadence Memory Model core architecture, interface, and use model.

The HBM DRAM standard is an industry-leading, low-power, double-data-rate, high-data-width, volatile (DRAM) device memory standard for storage of system code, software applications, and user data. The HBM DRAM Memory Device Standard is designed to satisfy the performance and memory density demands of the leading-edge mobile devices. The Memory Model for HBM supports single-channel implementation version of the following HBM DRAM specifications, and can be used eight times to model a single 8-channel device.

Supported specification: The VIP for HBM Memory Model supports JEDEC specifications: JESD235B Rev 2.60 (HBM2E), JESD235B Rev 2.50 (HBM2) and JESD235 Rev 1.27 (HBM), JESD235C Rev 3.30

View Simulation VIP for HBM full description to...

- see the entire Simulation VIP for HBM datasheet

- get in contact with Simulation VIP for HBM Supplier

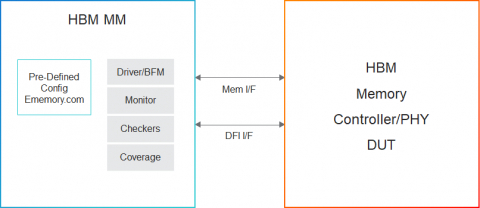

Block Diagram of the Simulation VIP for HBM Verification IP